LTM9003

LTM9003 is 12-Bit Digital Pre-Distortion Receiver Subsystem manufactured by Linear Technology.

Electrical Specifications Subject to Change

..

LTM9003 12-Bit Digital Pre-Distortion Receiver Subsystem DESCRIPTION

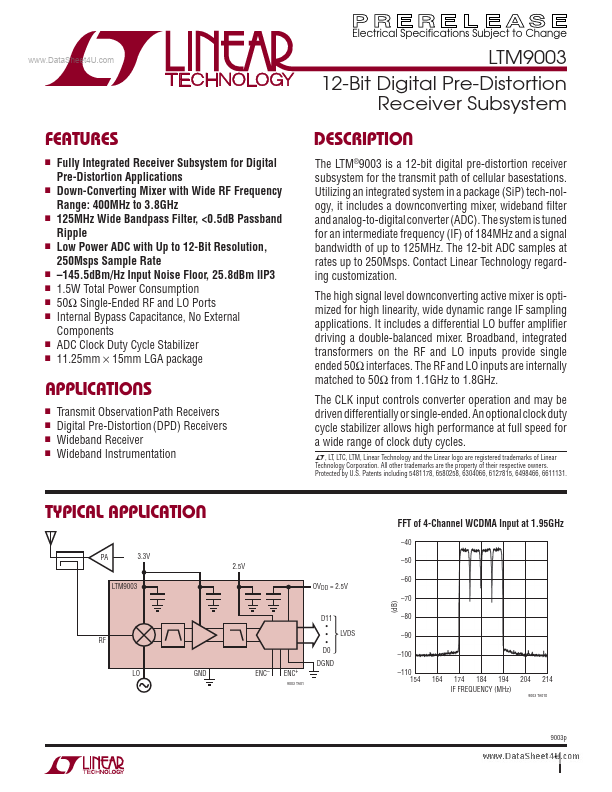

The LTM®9003 is a 12-bit digital pre-distortion receiver subsystem for the transmit path of cellular basestations. Utilizing an integrated system in a package (Si P) tech-nology, it includes a downconverting mixer, wideband filter and analog-to-digital converter (ADC). The system is tuned for an intermediate frequency (IF) of 184MHz and a signal bandwidth of up to 125MHz. The 12-bit ADC samples at rates up to 250Msps. Contact Linear Technology regarding customization. The high signal level downconverting active mixer is optimized for high linearity, wide dynamic range IF sampling applications. It includes a differential LO buffer amplifier driving a double-balanced mixer. Broadband, integrated transformers on the RF and LO inputs provide single ended 50Ω interfaces. The RF and LO inputs are internally matched to 50Ω from 1.1GHz to 1.8GHz. The CLK input controls converter operation and may be driven differentially or single-ended. An optional clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5481178, 6580258, 6304066, 6127815, 6498466, 6611131.

Features n n n n n n n n n n

Fully Integrated Receiver Subsystem for Digital Pre-Distortion Applications Down-Converting Mixer with Wide RF Frequency Range: 400MHz to 3.8GHz 125MHz Wide Bandpass Filter, <0.5d B Passband Ripple Low Power ADC with Up to 12-Bit Resolution, 250Msps Sample Rate

- 145.5d Bm/Hz Input Noise Floor, 25.8d Bm IIP3 1.5W Total Power Consumption 50Ω Single-Ended RF and LO Ports Internal Bypass Capacitance, No External ponents ADC Clock Duty Cycle Stabilizer 11.25mm × 15mm LGA package

APPLICATIONS n n n...