MX23L6430

Description

MROM is a synchronous high bandwidth mask programmable ROM with MXIC's high performance CMOS process technology and is organized either as 4M x 16 bits or 2M x 32 bits depending on polarity of WORD pin.

Key Features

- Switchable organization : 4M x 16 ( word mode ) or 2M x 32 ( double word mode )

- Power supply 3.0V ~ 3.6V

- All inputs are sampled at rising edge of system clock

- Read performance

- DQM for data-out masking

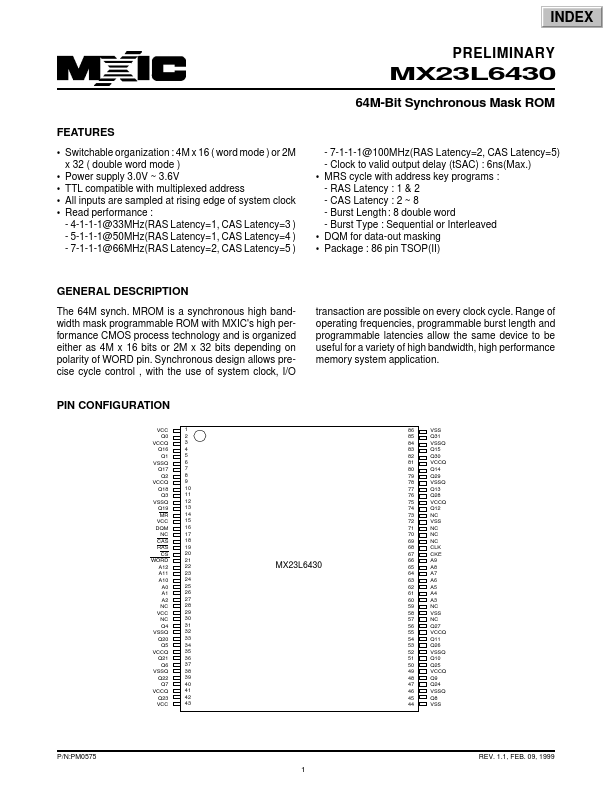

- Package : 86 pin TSOP(II)