SYS32256LK-15

SYS32256LK-15 is 256K x 32 SRAM MODULE manufactured by MOSAIC.

- Part of the SYS32256LK-12 comparator family.

- Part of the SYS32256LK-12 comparator family.

..

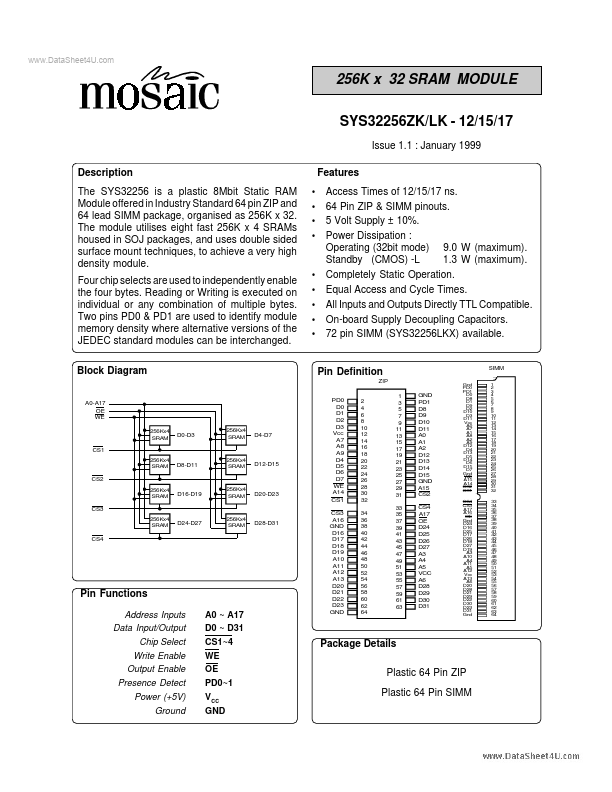

256K x 32 SRAM MODULE

SYS32256ZK/LK

- 12/15/17

Issue 1.1 : January 1999 Description The SYS32256 is a plastic 8Mbit Static RAM Module offered in Industry Standard 64 pin ZIP and 64 lead SIMM package, organised as 256K x 32. The module utilises eight fast 256K x 4 SRAMs housed in SOJ packages, and uses double sided surface mount techniques, to achieve a very high density module. Four chip selects are used to independently enable the four bytes. Reading or Writing is executed on individual or any bination of multiple bytes. Two pins PD0 & PD1 are used to identify module memory density where alternative versions of the JEDEC standard modules can be interchanged. Block...