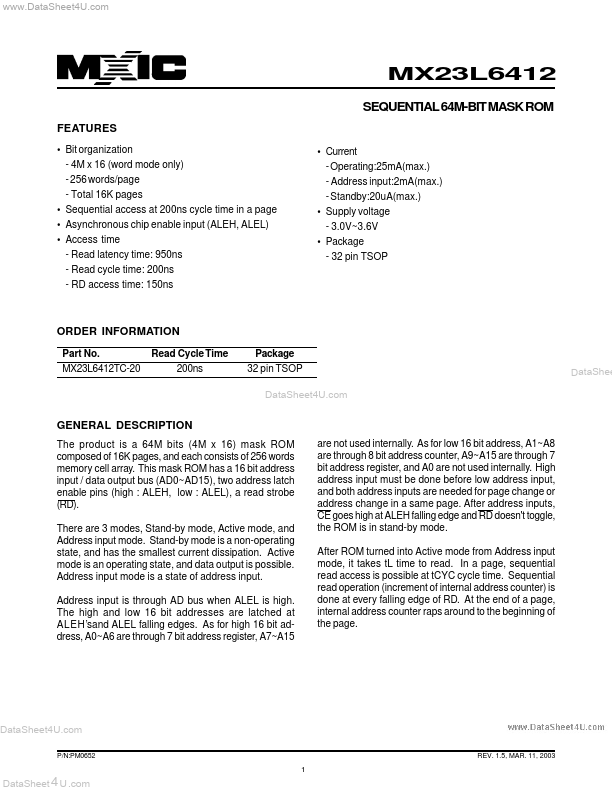

MX23L6412

Description

The product is a 64M bits (4M x 16) mask ROM composed of 16K pages, and each consists of 256 words memory cell array. This mask ROM has a 16 bit address input / data output bus (AD0~AD15), two address latch enable pins (high : ALEH, low : ALEL), a read strobe (RD).

Key Features

- Bit organization - 4M x 16 (word mode only) - 256 words/page - Total 16K pages

- Sequential access at 200ns cycle time in a page

- Asynchronous chip enable input (ALEH, ALEL)

- Access time - Read latency time: 950ns - Read cycle time: 200ns - RD access time: 150ns

- Current - Operating:25mA(max.) - Address input:2mA(max.) - Standby:20uA(max.)

- Supply voltage - 3.0V~3.6V

- Package - 32 pin TSOP