DS33R41

Description

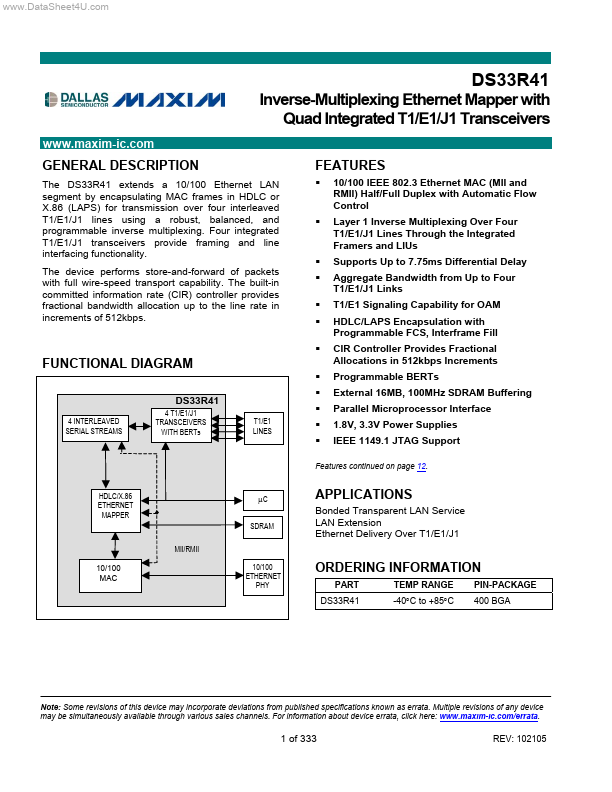

The DS33R41 extends a 10/100 Ethernet LAN segment by encapsulating MAC frames in HDLC or X.86 (LAPS) for transmission over four interleaved T1/E1/J1 lines using a robust, balanced, and programmable inverse multiplexing.

Key Features

- HDLC/X.86 ETHERNET MAPPER µC SDRAM MII/RMII