MAX3991 Overview

Description

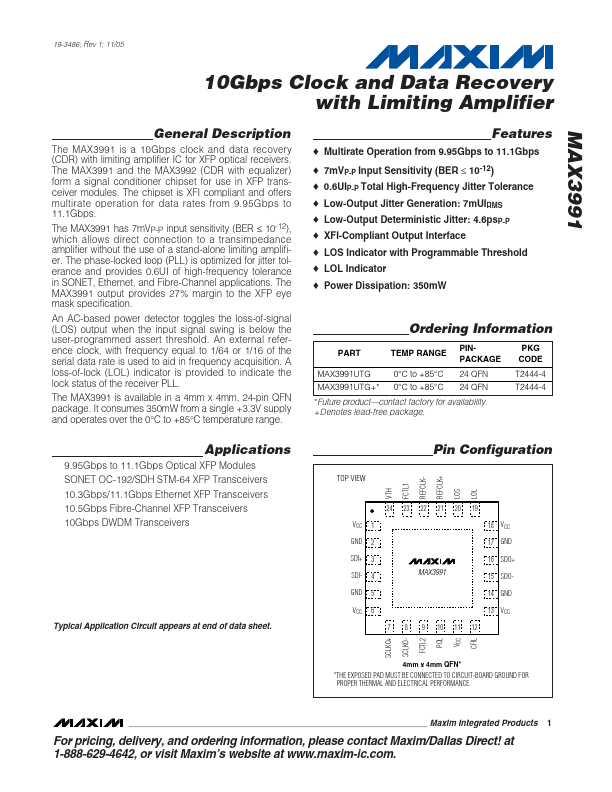

The MAX3991 is a 10Gbps clock and data recovery (CDR) with limiting amplifier IC for XFP optical receivers. The MAX3991 and the MAX3992 (CDR with equalizer) form a signal conditioner chipset for use in XFP transceiver modules.

Key Features

- Multirate Operation from 9.95Gbps to 11.1Gbps

- 7mVP-P Input Sensitivity (BER ≤ 10-12)

- 0.6UIP-P Total High-Frequency Jitter Tolerance

- Low-Output Jitter Generation: 7mUIRMS

- Low-Output Deterministic Jitter: 4.6psP-P

- XFI-Compliant Output Interface

- LOS Indicator with Programmable Threshold

- LOL Indicator

- Power Dissipation: 350mW MAX3991