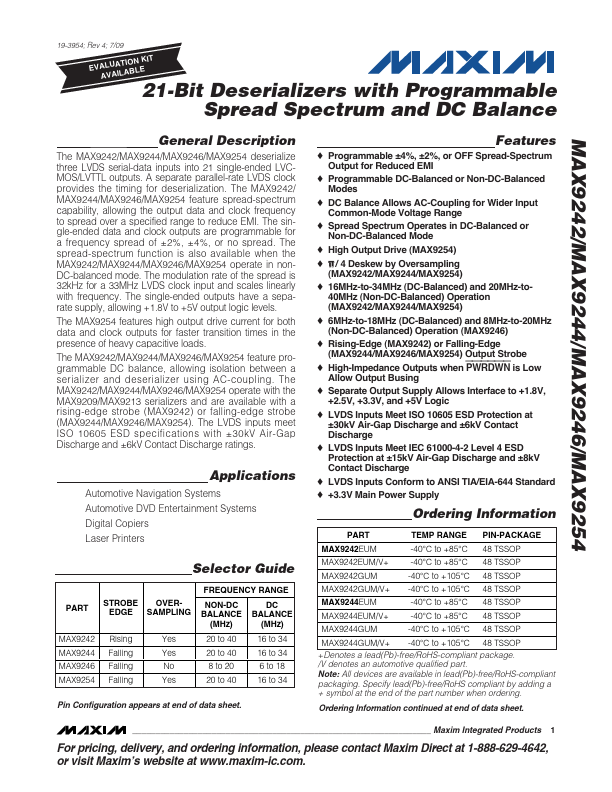

MAX9254

Description

The MAX9242/MAX9244/MAX9246/MAX9254 deserialize three LVDS serial-data inputs into 21 single-ended LVCMOS/ LVTTL outputs. A separate parallel-rate LVDS clock provides the timing for deserialization.

Key Features

- Programmable ±4%, ±2%, or OFF Spread-Spectrum Output for Reduced EMI

- Programmable DC-Balanced or Non-DC-Balanced Modes

- DC Balance Allows AC-Coupling for Wider Input mon-Mode Voltage Range

- Spread Spectrum Operates in DC-Balanced or Non-DC-Balanced Mode

- High Output Drive (MAX9254)

- High-Impedance Outputs when PWRDWN is Low Allow Output Busing

- Separate Output Supply Allows Interface to +1.8V, +2.5V, +3.3V, and +5V Logic

- LVDS Inputs Meet ISO 10605 ESD Protection at ±30kV Air-Gap Discharge and ±6kV Contact Discharge

- LVDS Inputs Meet IEC 61000-4-2 Level 4 ESD Protection at ±15kV Air-Gap Discharge and ±8kV Contact Discharge

- LVDS Inputs Conform to ANSI TIA/EIA-644 Standard