MAX9476

Key Features

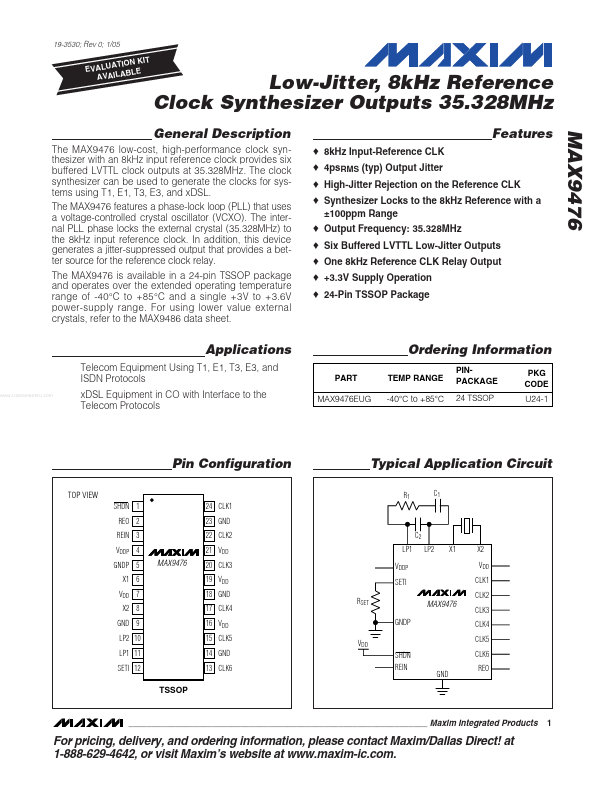

- The clock synthesizer can be used to generate the clocks for systems using T1, E1, T3, E3, and xDSL

- The MAX9476 features a phase-lock loop (PLL) that uses a voltage-controlled crystal oscillator (VCXO)

- The internal PLL phase locks the external crystal (35.328MHz) to the 8kHz input reference clock

- In addition, this device generates a jitter-suppressed output that provides a better source for the reference clock relay

- For using lower value external crystals, refer to the MAX9486 data sheet