DS28E01-100

Description

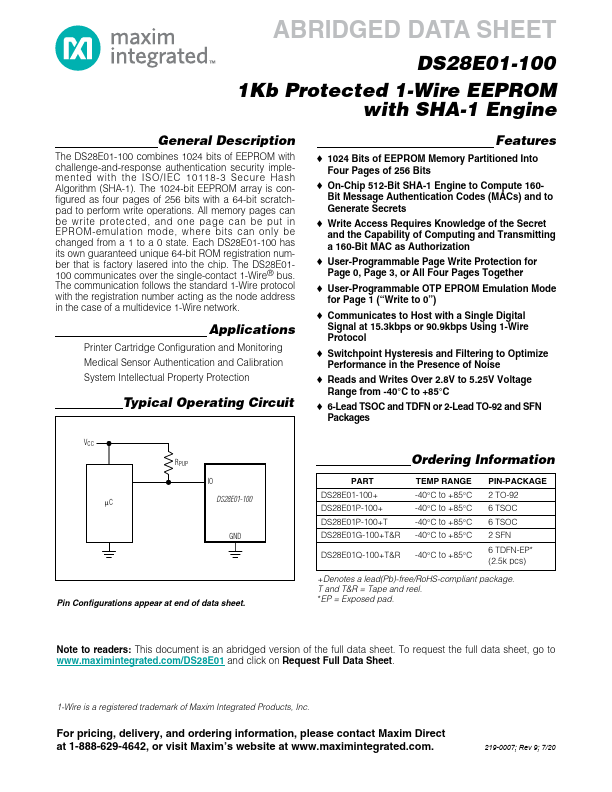

The DS28E01-100 combines 1024 bits of EEPROM with challenge-and-response authentication security implemented with the ISO/IEC 10118-3 Secure Hash Algorithm (SHA-1). The 1024-bit EEPROM array is configured as four pages of 256 bits with a 64-bit scratchpad to perform write operations.

Key Features

- 1024 Bits of EEPROM Memory Partitioned Into Four Pages of 256 Bits

- On-Chip 512-Bit SHA-1 Engine to Compute 160Bit Message Authentication Codes (MACs) and to Generate Secrets

- Write Access Requires Knowledge of the Secret and the Capability of Computing and Transmitting a 160-Bit MAC as Authorization

- User-Programmable Page Write Protection for Page 0, Page 3, or All Four Pages Together

- User-Programmable OTP EPROM Emulation Mode for Page 1 (“Write to 0”)

- Communicates to Host with a Single Digital Signal at 15.3kbps or 90.9kbps Using 1-Wire Protocol

- Switchpoint Hysteresis and Filtering to Optimize Performance in the Presence of Noise

- Reads and Writes Over 2.8V to 5.25V Voltage Range from -40°C to +85°C

- 6-Lead TSOC and TDFN or 2-Lead TO-92 and SFN Packages