DSSHA1

Description

The DSSHA1 coprocessor with 64-byte RAM is a synthesizable register transfer level (RTL) implementation of the FIPS 180-3 Secure Hash Algorithm (SHA-1), eliminating the need to develop software to perform the complex SHA-1 computation required for authenticating SHA-1 devices. The DSSHA1 can compute SHA-1 message authentication codes (MACs) for use with Maxim SHA-1 devices, such as the DS1963S, DS1961S, DS28E10, DS28E02, DS2460, DS28CN01, and DS28E01-100.

Key Features

- SHA-1 Computations Within 670 Clock Cycles (13.4µs at a Typical Frequency of 50MHz)

- Area Estimate is 102,256µm2 in TSMC CL018G (0.18µm Generic Process)

- Dedicated Hardware-Accelerated SHA-1 Engine for Generating MACs

- 64-Byte RAM for Message Input

- Five 32-Bit Registers to Read MAC Result

- Available in Synthesizable Verilog®

- Made as a Low-Level Module to be Instantiated by a Top-Level Module

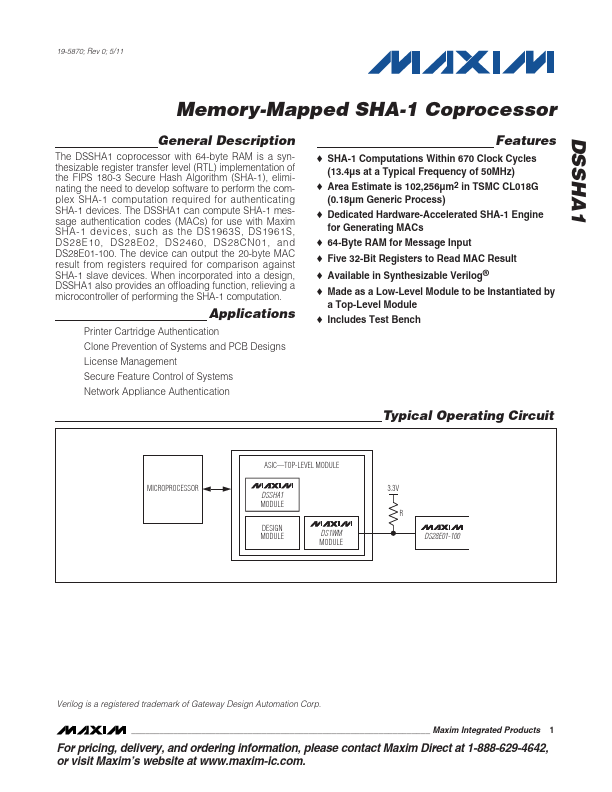

- Includes Test Bench Typical Operating Circuit