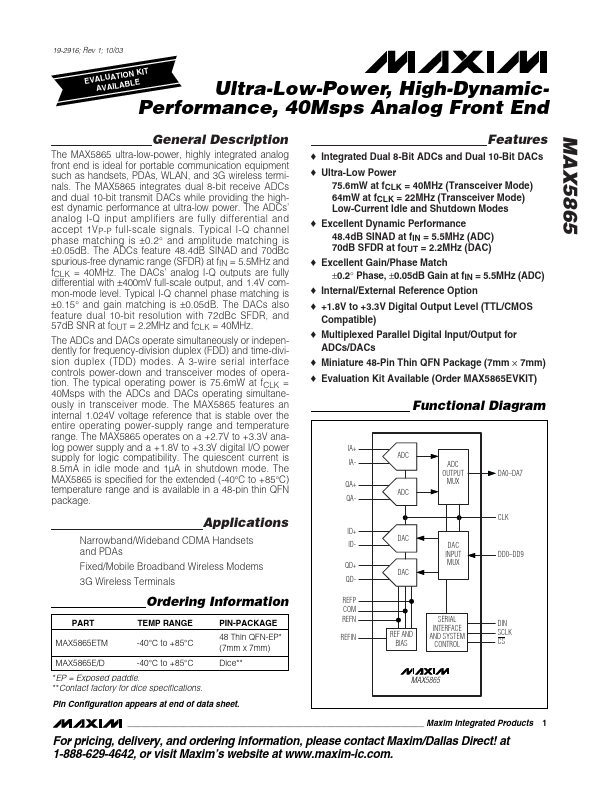

MAX5865 Description

The MAX5865 integrates dual 8-bit receive ADCs and dual 10-bit transmit DACs while providing the highest dynamic performance at ultra-low power. The ADCs’ analog I-Q input amplifiers are fully differential and accept 1VP-P full-scale signals. Typical I-Q channel phase matching is ±0.2° and amplitude matching is ±0.05dB.

MAX5865 Applications

- EP = Exposed paddle. --Contact factory for dice specifications. Pin Configu