Datasheet Summary

8051-Based MCU

MG87FEL52 Data Sheet

Version: A1.0

This document contains information on a new product under development by Megawin. Megawin reserves the right to change or discontinue this product without notice. Megawin Technology Co., Ltd. 2012 All rights reserved.

2014/03 version A1.0

MG87FEL52A Data Sheet

MEGAWIN

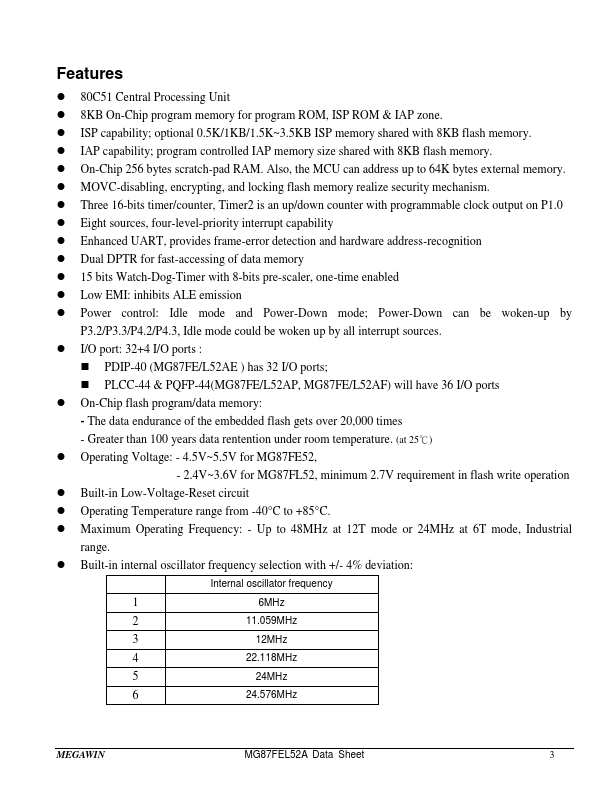

Features

- 80C51 Central Processing Unit

- 8KB On-Chip program memory for program ROM, ISP ROM & IAP zone.

- ISP capability; optional 0.5K/1KB/1.5K~3.5KB ISP memory shared with 8KB flash memory.

- IAP capability; program controlled IAP memory size shared with 8KB flash memory.

- On-Chip 256 bytes scratch-pad RAM. Also, the MCU can address up to 64K bytes external...