SY100E445

SY100E445 is 4-BIT SERIAL-to-PARALLEL CONVERTER manufactured by Micrel Semiconductor.

Micrel, Inc.

4-BIT SERIAL-to-PARALLEL CONVERTER

SY10E445

SY1S0YE10404E5445

Features s On-chip clock ÷4 and ÷8 s Extended 100E VEE range of

- 4.2V to

- 5.5V s 2.5Gb/s data rate capability s Differential clock and serial inputs s VBB output for single-ended use s Asynchronous data synchronization s Mode select to expand to 8 bits s Internal 75kΩ input pull-down resistors s Fully patible with Motorola MC10E/100E445 s Available in 28-pin PLCC package

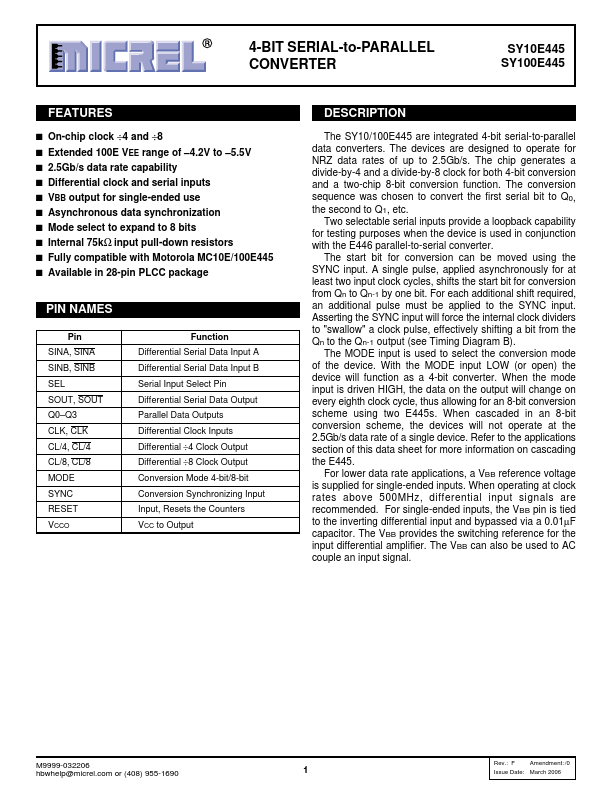

PIN NAMES

Pin SINA, SINA SINB, SINB SEL SOUT, SOUT Q0- Q3 CLK, CLK CL/4, CL/4 CL/8, CL/8 MODE SYNC RESET VCCO

Function Differential Serial Data Input A Differential Serial Data Input B Serial Input Select Pin Differential Serial Data Output Parallel Data Outputs Differential Clock Inputs Differential ÷4 Clock Output Differential ÷8 Clock Output Conversion Mode 4-bit/8-bit Conversion Synchronizing Input Input, Resets the Counters VCC to Output

DESCRIPTION

The SY10/100E445 are integrated 4-bit serial-to-parallel data converters. The devices are designed to operate for NRZ data rates of up to 2.5Gb/s. The chip generates a divide-by-4 and a divide-by-8 clock for both 4-bit conversion and a two-chip 8-bit conversion function. The conversion sequence was chosen to convert the first serial bit to Q0, the second to Q1, etc.

Two selectable serial inputs provide a loopback capability for testing purposes when the device is used in conjunction with the E446 parallel-to-serial converter.

The start bit for conversion can be moved using the SYNC input. A single pulse, applied asynchronously for at least two input clock cycles, shifts the start bit for conversion from Qn to Qn-1 by one bit. For each additional shift required, an additional pulse must be applied to the SYNC input. Asserting the SYNC input will force the internal clock dividers to "swallow" a clock pulse, effectively shifting a bit from the Qn to the Qn-1 output (see Timing Diagram B).

The MODE input is used to select the conversion mode of the device....