SY100H641A

SY100H641A is SINGLE SUPPLY 1:9 PECL-TO-TTL manufactured by Micrel Semiconductor.

- Part of the SY10H641A comparator family.

- Part of the SY10H641A comparator family.

..

SEMICONDUCTOR

SYNERGY

SINGLE SUPPLY 1:9 PECL-TO-TTL

Clock Works™ SY10H641A Clock Works™ SY100H641A

SY10H641A SY100H641A

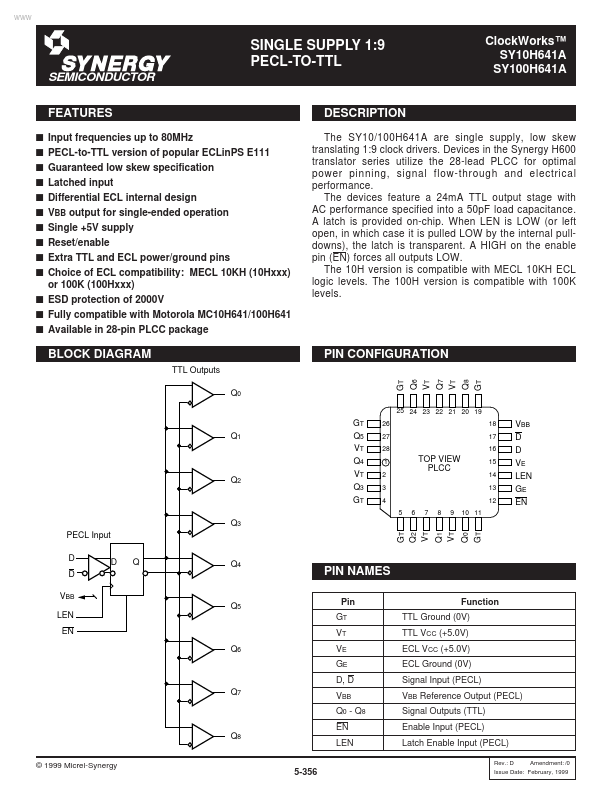

Features s s s s s s s s s s Input frequencies up to 80MHz PECL-to-TTL version of popular ECLin PS E111 Guaranteed low skew specification Latched input Differential ECL internal design VBB output for single-ended operation Single +5V supply Reset/enable Extra TTL and ECL power/ground pins Choice of ECL patibility: MECL 10KH (10Hxxx) or 100K (100Hxxx) s ESD protection of 2000V s Fully patible with Motorola MC10H641/100H641 s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100H641A are single supply, low skew translating 1:9 clock drivers. Devices in the Synergy H600 translator series utilize the 28-lead PLCC for optimal power pinning, signal flow-through and electrical performance. The devices feature a 24m A TTL output stage with AC performance specified into a 50p F load capacitance. A latch is provided on-chip. When LEN is LOW (or left open, in which case it is pulled LOW by the internal pulldowns), the latch is transparent. A HIGH on the enable pin (EN) forces all outputs LOW. The 10H version is patible with MECL 10KH ECL logic levels. The 100H version is patible with 100K levels.

BLOCK DIAGRAM

TTL Outputs Q0

PIN CONFIGURATION

Q6 VT Q7 VT Q8 GT

18 17 16

25 24 23 22 21 20 19

Q1

Q2

GT Q5 VT Q4 VT Q3 GT

26 27 28 1 2 3 4 5 6 7 8 9 10 11

TOP VIEW PLCC

15 14 13 12

VBB D D VE LEN GE EN

Q3 GT Q2 VT Q1 VT Q0 GT PECL Input D D VBB Q5 LEN EN Q6 D Q Q4

PIN NAMES

Pin GT VT VE GE D, D Function TTL Ground (0V) TTL VCC (+5.0V) ECL VCC (+5.0V) ECL Ground (0V) Signal Input (PECL) VBB Reference Output (PECL) Signal Outputs (TTL) Enable Input (PECL) Latch Enable Input (PECL)

Rev.: D Amendment: /0 Issue Date: February, 1999

Q7

VBB Q0

- Q8...