SY10E143

SY10E143 is 9-BIT HOLD REGISTER manufactured by Micrel Semiconductor.

- Part of the SY100E143 comparator family.

- Part of the SY100E143 comparator family.

Micrel, Inc.

NOT REMENDED FOR NEW DESIGNS

9-BIT HOLD REGISTER

SY1S0YE10104E3143 SY100E143

Features s 700MHz min. operating frequency s Extended 100E VEE range of

- 4.2V to

- 5.5V s 9 bits wide for byte-parity applications s Asynchronous Master Reset s Dual clocks s Fully patible with industry standard 10KH,

100K ECL levels s Internal 75kΩ input pulldown resistors s Fully patible with Motorola MC10E/100E143 s Available in 28-pin PLCC package

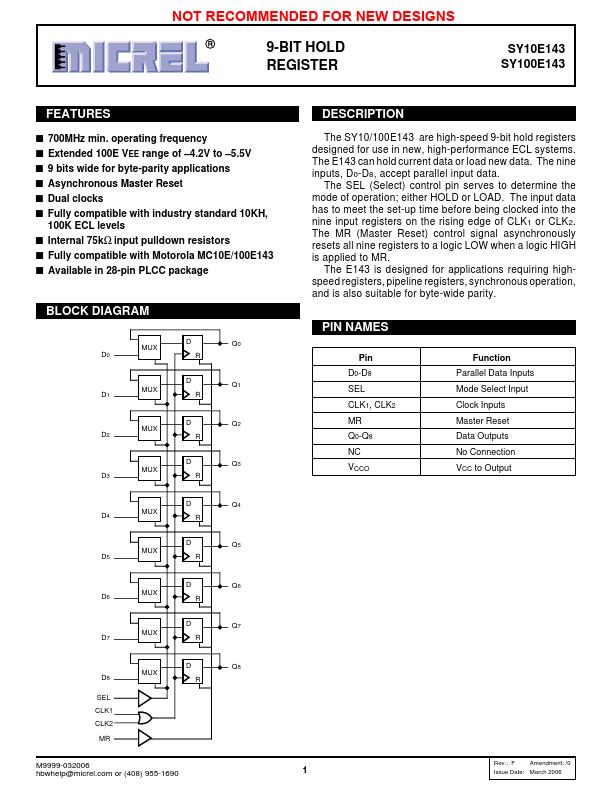

BLOCK DIAGRAM

D MUX D0 R

D1 MUX

D MUX D2 R

MUX D3

D4 MUX

MUX D5

D6 MUX

D7 MUX

D8

SEL CLK1 CLK2

M9999-032006 hbwhelp@micrel. or (408) 955-1690

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

DESCRIPTION

The SY10/100E143 are high-speed 9-bit hold registers designed for use in new, high-performance ECL systems. The E143 can hold current data or load new data. The nine inputs, D0-D8, accept parallel input data.

The SEL (Select) control pin serves to determine the mode of operation; either HOLD or LOAD. The input data has to meet the set-up time before being clocked into the nine input registers on the rising edge of CLK1 or CLK2. The MR (Master Reset) control signal asynchronously resets all nine registers to a logic LOW when a logic HIGH is applied to MR.

The E143 is designed for applications requiring highspeed registers, pipeline registers, synchronous operation, and is also suitable for byte-wide parity.

PIN NAMES

Pin D0-D8 SEL CLK1, CLK2 MR Q0-Q8 NC VCCO

Function Parallel Data Inputs Mode Select Input Clock Inputs Master Reset Data Outputs No Connection VCC to Output

Rev.: F Amendment: /0

1 Issue Date: March...