SY10E160

SY10E160 is 12-BIT PARITY GENERATOR/CHECKER manufactured by Micrel Semiconductor.

- Part of the SY100E160 comparator family.

- Part of the SY100E160 comparator family.

12-BIT PARITY GENERATOR/CHECKER

SY10E160 SY100E160

Features s Provides odd-HIGH parity of 12 inputs s Extended 100E VEE range of

- 4.2V to

- 5.5V s s s s s s Output register with Shift/Hold capability 900ps max. D to Q, /Q output Enable control Asynchronous Register Reset Differential outputs Fully patible with industry standard 10KH, 100K ECL levels s Internal 75KΩ input pulldown resistors s Fully patible with Motorola MC10E/100E160 s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E160 are high-speed, 12-bit parity generator/checkers with differential outputs, for use in new, high-performance ECL systems. The output Q takes on a logic HIGH value only when an odd number of inputs are at a logic HIGH. A logic HIGH on the enable input (EN) forces the output Q to a logic LOW. An additional feature of the E160 is the output register. Two multiplexers and their associated signals control the register input by providing the option of holding present data, loading the new parity data or shifting external data in. To hold the present data, the Hold signal (HOLD) must be at a logic LOW level. If the HOLD signal is at a logic HIGH, the data present at the Q output is passed through the first multiplexer. Taking the Shift signal (SHIFT) to a logic HIGH will shift the data at the S-IN pin into the output register. If the SHIFT signal is at a logic LOW, the output of the first multiplexer is then passed through to the register. The register itself is clocked on the rising edge of CLK1 or CLK2 (or both). The presence of a logic HIGH on the reset pin (R) forces the register output Y to a logic LOW.

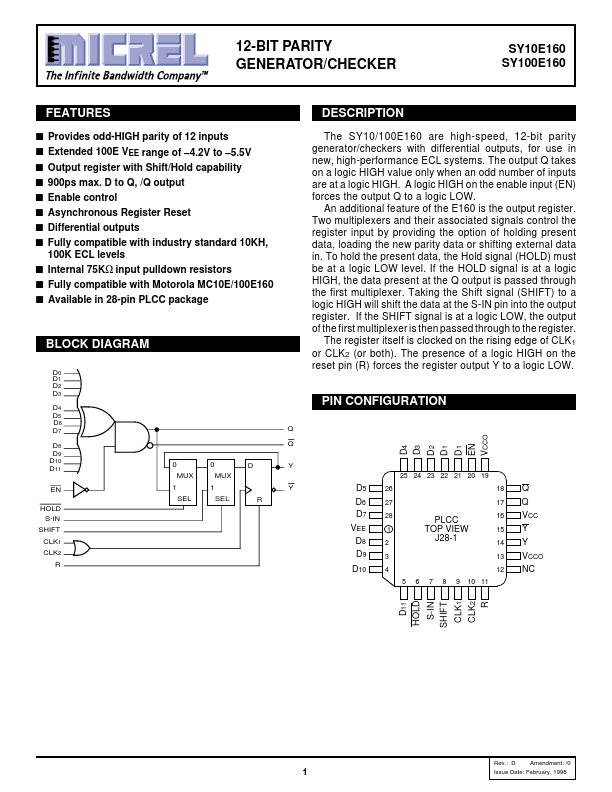

BLOCK DIAGRAM

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 EN HOLD S-IN SHIFT CLK1 CLK2 R

PIN CONFIGURATION

D4 D3

D2 D1

0 MUX 1 SEL

0 MUX 1 SEL

25 24 23 22 21 20 19

D5 D6 D7 VEE D8 D9 D10

D1

EN VCCO

26 27 28 1 2 3 4 5 6 7 8 9 10 11

18 17

Q Q VCC Y Y VCCO NC

PLCC TOP VIEW J28-1

16 15 14 13 12

D11 HOLD

S-IN SHIFT

CLK1

CLK2 R

Rev.:...