ML2264 Overview

Description

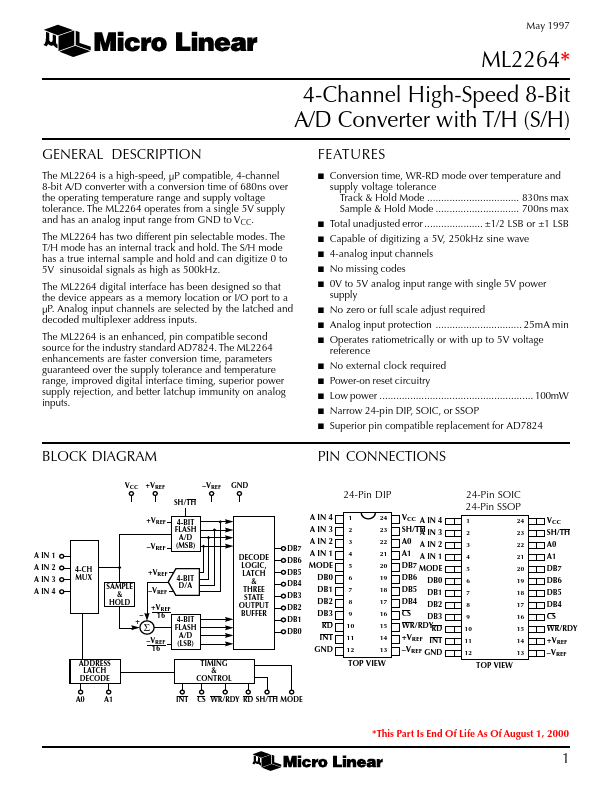

The ML2264 is a high-speed, µP compatible, 4-channel 8-bit A/D converter with a conversion time of 680ns over the operating temperature range and supply voltage tolerance. The ML2264 operates from a single 5V supply and has an analog input range from GND to VCC.

Key Features

- s s s s s s s s s s s s s s Conversion time, WR-RD mode over temperature and supply voltage tolerance Track & Hold Mode

- 830ns max Sample & Hold Mode

- 700ns max Total unadjusted error

- 25mA min Operates ratiometrically or with up to 5V voltage reference No external clock required Power-on reset circuitry Low power

- 100mW Narrow 24-pin DIP, SOIC, or SSOP Superior pin compatible replacement for AD7824