PIC18F26K22

PIC18F26K22 is High-Performance Microcontrollers manufactured by Microchip Technology.

- Part of the PIC18F23K22 comparator family.

- Part of the PIC18F23K22 comparator family.

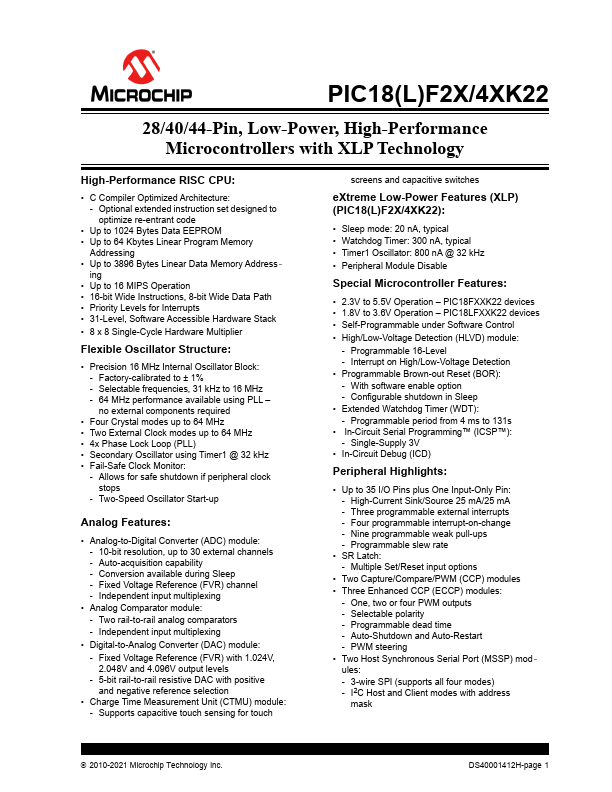

PIC18(L)F2X/4XK22

28/40/44-Pin, Low-Power, High-Performance Microcontrollers with XLP Technology

High-Performance RISC CPU:

- C piler Optimized Architecture:

- Optional extended instruction set designed to optimize re-entrant code

- Up to 1024 Bytes Data EEPROM

- Up to 64 Kbytes Linear Program Memory

Addressing

- Up to 3896 Bytes Linear Data Memory Address- ing

- Up to 16 MIPS Operation

- 16-bit Wide Instructions, 8-bit Wide Data Path

- Priority Levels for Interrupts

- 31-Level, Software Accessible Hardware Stack

- 8 x 8 Single-Cycle Hardware Multiplier

Flexible Oscillator Structure:

- Precision 16 MHz Internal Oscillator Block:

- Factory-calibrated to ± 1%

- Selectable frequencies, 31...