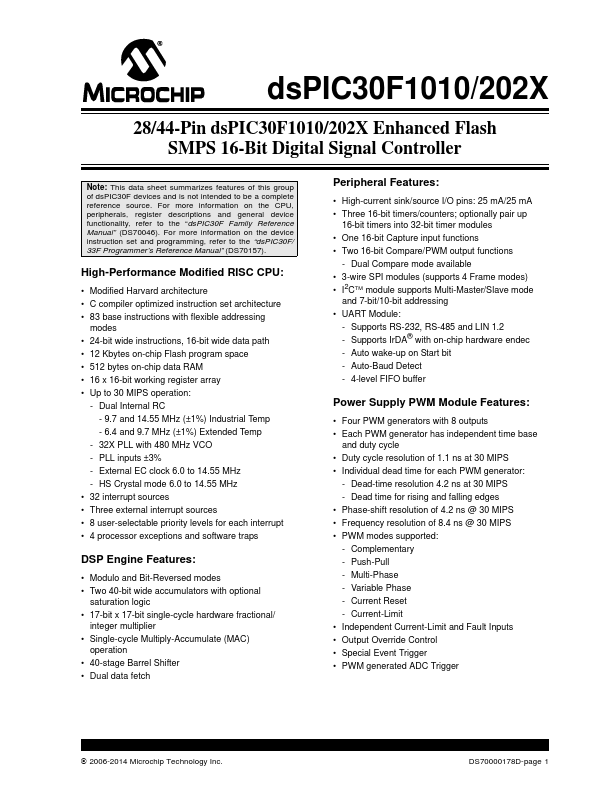

DSPIC30F2020

Key Features

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- 83 base instructions with flexible addressing modes

- 24-bit wide instructions, 16-bit wide data path

- 12 Kbytes on-chip Flash program space

- 512 bytes on-chip data RAM

- 16 x 16-bit working register array

- Up to 30 MIPS operation: - Dual Internal RC - 9.7 and 14.55 MHz (±1%) Industrial Temp - 6.4 and 9.7 MHz (±1%)