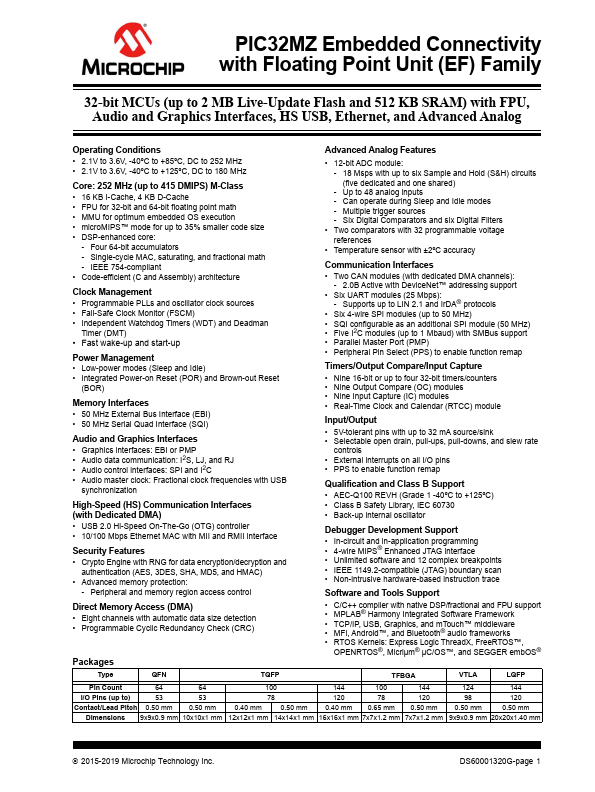

PIC32MZ2048EFH100

Key Features

- 16 KB I-Cache, 4 KB D-Cache

- FPU for 32-bit and 64-bit floating point math

- MMU for optimum embedded OS execution

- microMIPS™ mode for up to 35% smaller code size

- DSP-enhanced core

- Four 64-bit accumulators - Single-cycle MAC, saturating, and fractional math - IEEE 754-pliant

- Code-efficient (C and Assembly) architecture

- Programmable PLLs and oscillator clock sources

- Fail-Safe Clock Monitor (FSCM)

- Independent Watchdog Timers (WDT) and Deadman