SY100EL52

Overview

The SY100EL52 is a differential data, differential clock D flip-flop. Data enters the master portion of the flip-flop when the clock is low and is transferred to the slave, then the outputs, upon a positive transition of the clock.

- 365 ps Propagation Delay (typical)

- 2.8 GHz Toggle Frequency (typical)

- Internal 75 kΩ Input Pull-Down Resistors

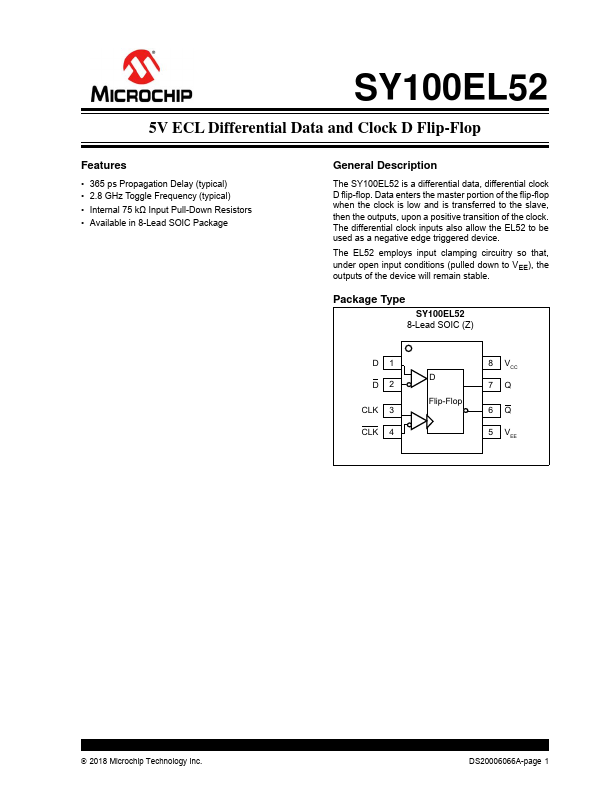

- Available in 8-Lead SOIC Package