TP2502 Overview

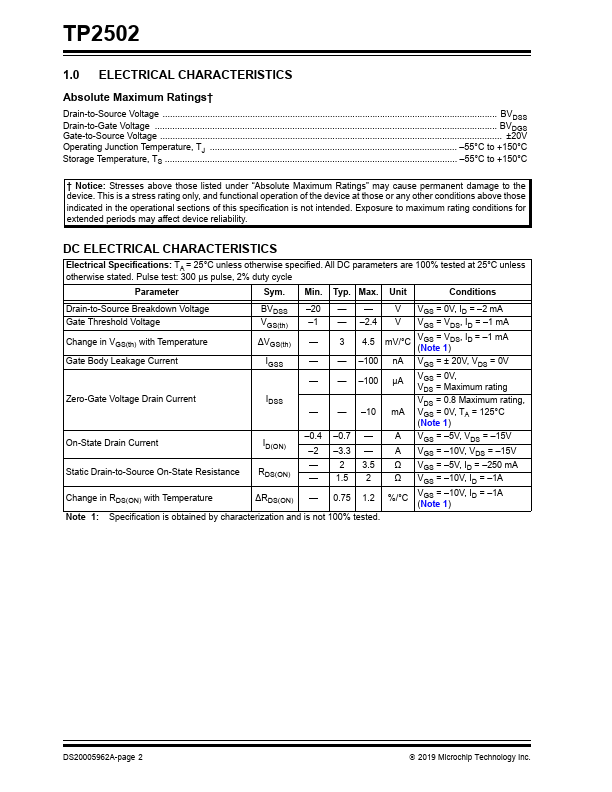

The TP2502 low-threshold Enhancement-mode (normally-off) transistor uses a vertical DMOS structure and a well-proven silicon-gate manufacturing process. This bination produces a device with the power handling capabilities of bipolar transistors and the high input impedance and positive temperature coefficient inherent in MOS devices. Characteristic of all MOS structures, this device is free from thermal runaway and...

TP2502 Key Features

- 2.4V Maximum Low Threshold

- High Input Impedance

- 125 pF Maximum Low Input Capacitance

- Fast Switching Speeds

- Low On-Resistance

- Free from Secondary Breakdown

- Low Input and Output Leakage

TP2502 Applications

- Logic-Level Interfaces (Ideal for TTL and CMOS)