dsPIC33EP256MU810

dsPIC33EP256MU810 is 16-bit Microcontrollers and Digital Signal Controllers manufactured by Microchip Technology.

- Part of the dsPIC33EP256MU806 comparator family.

- Part of the dsPIC33EP256MU806 comparator family.

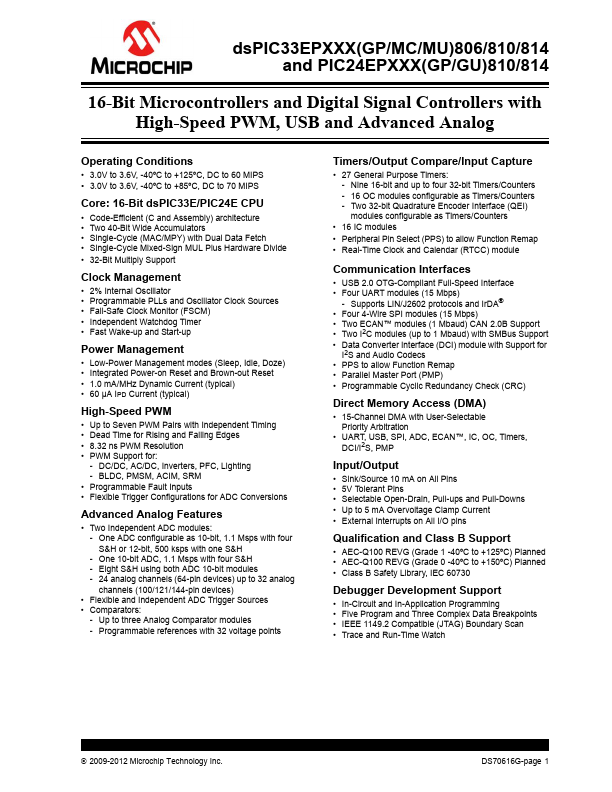

ds PIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

16-Bit Microcontrollers and Digital Signal Controllers with High-Speed PWM, USB and Advanced Analog

Operating Conditions

- 3.0V to 3.6V, -40ºC to +125ºC, DC to 60 MIPS

- 3.0V to 3.6V, -40ºC to +85ºC, DC to 70 MIPS

Core: 16-Bit ds PIC33E/PIC24E CPU

- Code-Efficient (C and Assembly) architecture

- Two 40-Bit Wide Accumulators

- Single-Cycle (MAC/MPY) with Dual Data Fetch

- Single-Cycle Mixed-Sign MUL Plus Hardware Divide

- 32-Bit Multiply Support

Clock Management

- 2% Internal Oscillator

- Programmable PLLs and Oscillator Clock Sources

- Fail-Safe Clock Monitor (FSCM)

- Independent Watchdog Timer

- Fast Wake-up and Start-up

Power Management

- Low-Power Management modes (Sleep, Idle, Doze)

- Integrated Power-on Reset and Brown-out Reset

- 1.0 m A/MHz Dynamic Current (typical)

- 60 µA IPD Current (typical)

High-Speed PWM

- Up to Seven PWM Pairs with Independent Timing

- Dead Time for Rising and Falling Edges

- 8.32 ns PWM Resolution

- PWM Support for:

- DC/DC, AC/DC, Inverters, PFC, Lighting

- BLDC, PMSM, ACIM, SRM

- Programmable Fault...