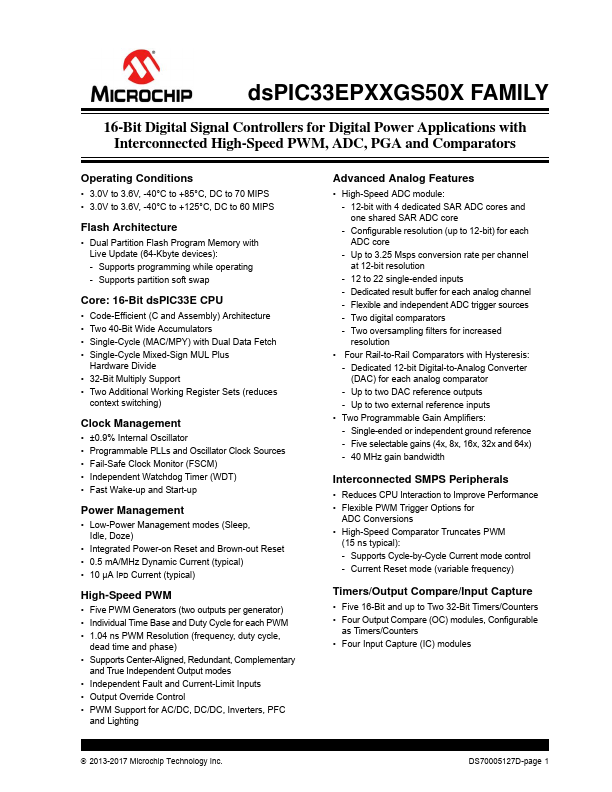

dsPIC33EP64GS506

dsPIC33EP64GS506 is 16-Bit Digital Signal Controllers manufactured by Microchip Technology.

- Part of the dsPIC33EP16GS502 comparator family.

- Part of the dsPIC33EP16GS502 comparator family.

Features

- High-Speed ADC module:

- 12-bit with 4 dedicated SAR ADC cores and one shared SAR ADC core

- Configurable resolution (up to 12-bit) for each ADC core

- Up to 3.25 Msps conversion rate per channel at 12-bit resolution

- 12 to 22 single-ended inputs

- Dedicated result buffer for each analog channel

- Flexible and independent ADC trigger sources

- Two digital parators

- Two oversampling filters for increased resolution

- Four Rail-to-Rail parators with Hysteresis:

- Dedicated 12-bit Digital-to-Analog Converter (DAC) for each analog parator

- Up to two DAC reference outputs

- Up to two external reference inputs

- Two Programmable Gain Amplifiers:

- Single-ended or independent ground reference

- Five selectable gains (4x, 8x, 16x, 32x and 64x)

- 40 MHz gain bandwidth

Interconnected SMPS Peripherals

- Reduces CPU Interaction to Improve Performance

- Flexible PWM Trigger Options for

ADC Conversions

- High-Speed parator Truncates PWM

(15 ns typical):

- Supports Cycle-by-Cycle Current mode control

- Current Reset mode (variable frequency)

Timers/Output pare/Input Capture

- Five 16-Bit and up to Two 32-Bit Timers/Counters

- Four Output pare (OC) modules, Configurable as Timers/Counters

- Four Input Capture (IC) modules

2013-2017 Microchip Technology Inc.

DS70005127D-page 1 ds PIC33EPXXGS50X FAMILY munication Interfaces

- Two UART modules (15 Mbps):

- Supports LIN/J2602 protocols and Ir DA®

- Two 4-Wire SPI modules (15 Mbps)

- Two...