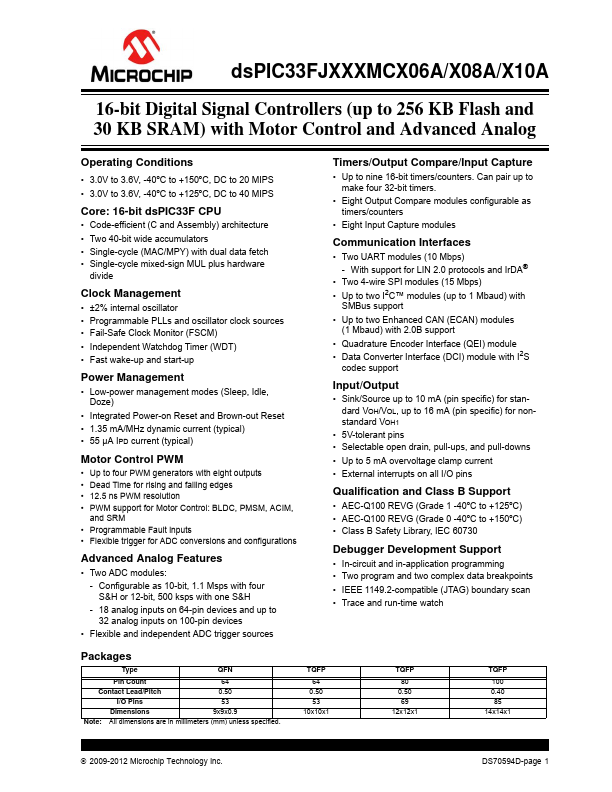

dsPIC33FJ64MC706A

Key Features

- Two ADC modules

- Configurable as 10-bit, 1.1 Msps with four S&H or 12-bit, 500 ksps with one S&H

- 18 analog inputs on 64-pin devices and up to 32 analog inputs on 100-pin devices

- Flexible and independent ADC trigger sources Timers/Output pare/Input Capture

- Up to nine 16-bit timers/counters. Can pair up to make four 32-bit timers

- Eight Output pare modules configurable as timers/counters

- Eight Input Capture modules munication Interfaces

- Two UART modules (10 Mbps)

- With support for LIN 2.0 protocols and IrDA®

- Two 4-wire SPI modules (15 Mbps)