MT2854M16B1LL

MT2854M16B1LL is FLASH MEMORY manufactured by Micron Technology.

..

ADVANCE‡

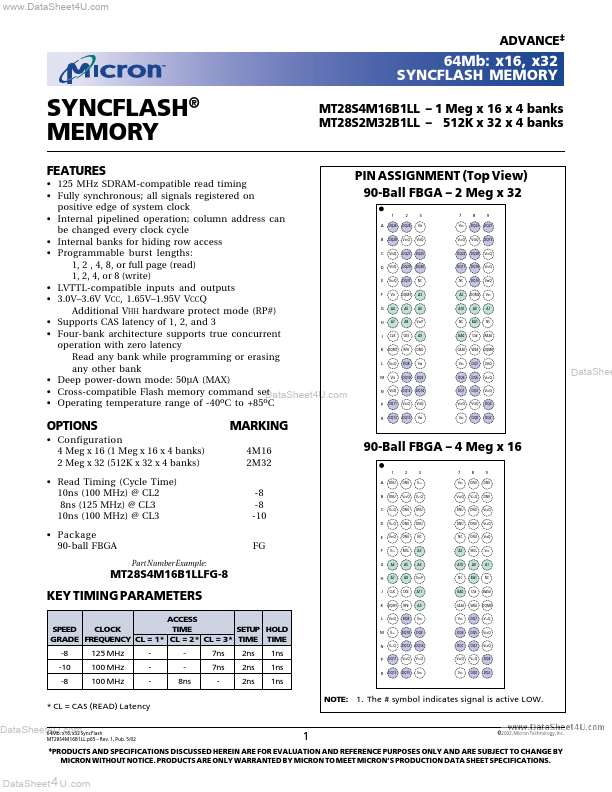

64Mb: x16, x32 SYNCFLASH MEMORY

SYNCFLASH® MEMORY

Features

MT28S4M16B1LL

- 1 Meg x 16 x 4 banks MT28S2M32B1LL

- 512K x 32 x 4 banks

- 125 MHz SDRAM-patible read timing

- Fully synchronous; all signals registered on positive edge of system clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access

- Programmable burst lengths: 1, 2 , 4, 8, or full page (read) 1, 2, 4, or 8 (write)

- LVTTL-patible inputs and outputs

- 3.0V- 3.6V VCC, 1.65V- 1.95V VCCQ Additional VHH hardware protect mode (RP#)

- Supports CAS latency of 1, 2, and 3

- Four-bank architecture supports true concurrent operation...