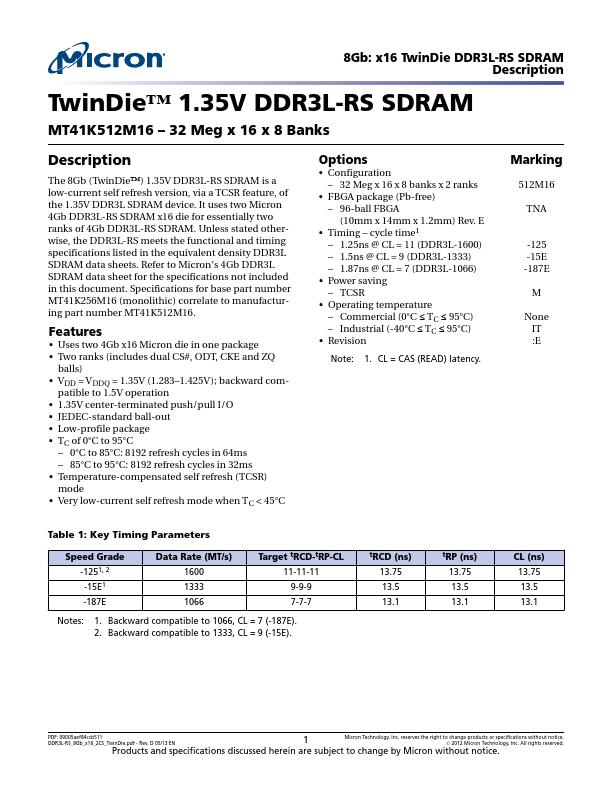

MT41K512M16 Overview

Key Features

- Uses two 4Gb x16 Micron die in one package

- Two ranks (includes dual CS#, ODT, CKE and ZQ balls)

- VDD = V DDQ = 1.35V (1.283–1.425V); backward compatible to 1.5V operation

- 1.35V center-terminated push/pull I/O

- JEDEC-standard ball-out

- Low-profile package

- TC of 0°C to 95°C – 0°C to 85°C: 8192 refresh cycles in 64ms – 85°C to 95°C: 8192 refresh cycles in 32ms

- Temperature-compensated self refresh (TCSR) mode

- Backward compatible to 1066, CL = 7 (-187E)