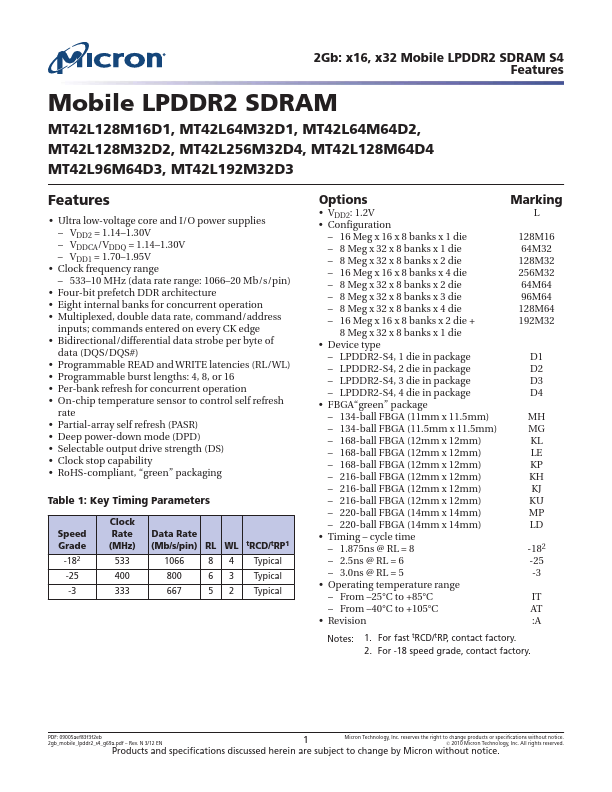

MT42L64M64D2

Key Features

- Mobile LPDDR2 SDRAM

- Ultra low-voltage core and I/O power supplies – VDD2 = 1.14–1.30V – VDDCA/VDDQ = 1.14–1.30V – VDD1 = 1.70–1.95V

- Clock frequency range – 533–10 MHz (data rate range: 1066–20 Mb/s/pin)

- Four-bit prefetch DDR architecture

- Eight internal banks for concurrent operation

- Multiplexed, double data rate, mand/address inputs; mands entered on every CK edge

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable READ and WRITE latencies (RL/WL)

- Per-bank refresh for concurrent operation

- On-chip temperature sensor to control self refresh rate