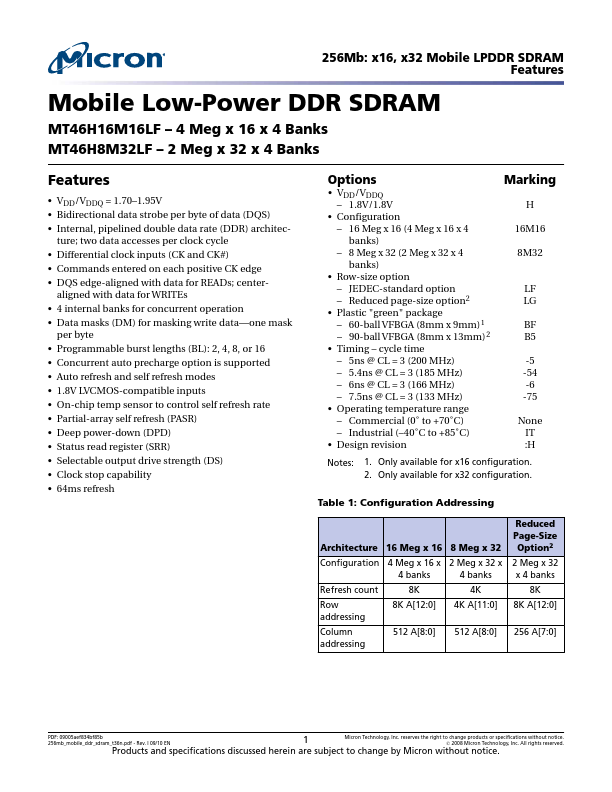

MT46H16M16LF

Key Features

- Bidirectional data strobe per byte of data (DQS)

- Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- mands entered on each positive CK edge

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- Four internal banks for concurrent operation

- Data masks (DM) for masking write data–one mask per byte

- Programmable burst lengths: 2, 4, 8, 16 or full page

- Concurrent auto precharge option is supported

- Auto refresh and self refresh modes