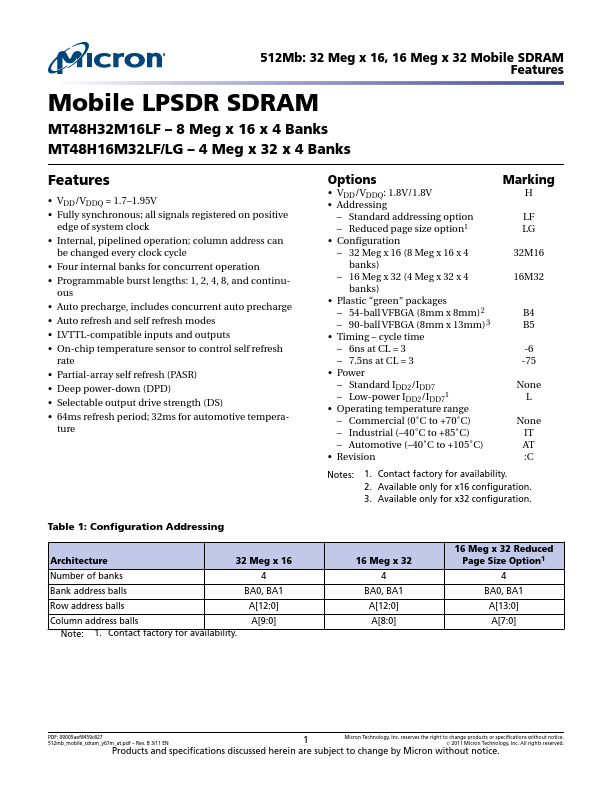

MT48H32M16LF

Key Features

- Mobile LPSDR SDRAM

- VDD/VDDQ = 1.7–1.95V

- Fully synchronous; all signals registered on positive edge of system clock

- Internal, pipelined operation; column address can be changed every clock cycle

- Four internal banks for concurrent operation

- Programmable burst lengths: 1, 2, 4, 8, and continuous

- Auto precharge, includes concurrent auto precharge

- Auto refresh and self refresh modes

- On-chip temperature sensor to control self refresh rate

- Partial-array self refresh (PASR)