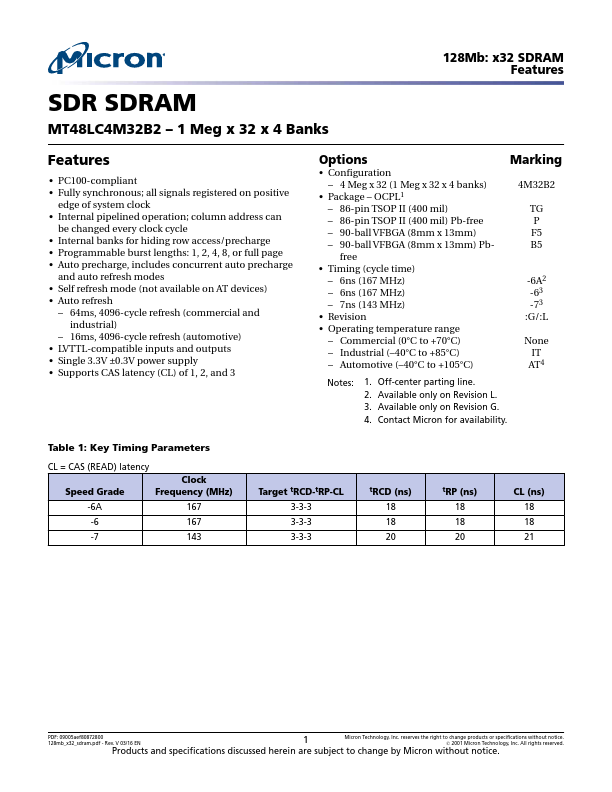

MT48LC4M32B2

Key Features

- PC100-pliant

- Fully synchronous; all signals registered on positive

- Internal pipelined operation; column address can

- Internal banks for hiding row access/precharge

- Programmable burst lengths: 1, 2, 4, 8, or full page

- Auto precharge, includes concurrent auto precharge

- Self refresh mode (not available on AT devices)

- Auto refresh

- Single 3.3V ±0.3V power supply

- Supports CAS latency (CL) of 1, 2, and 3