Datasheet Summary

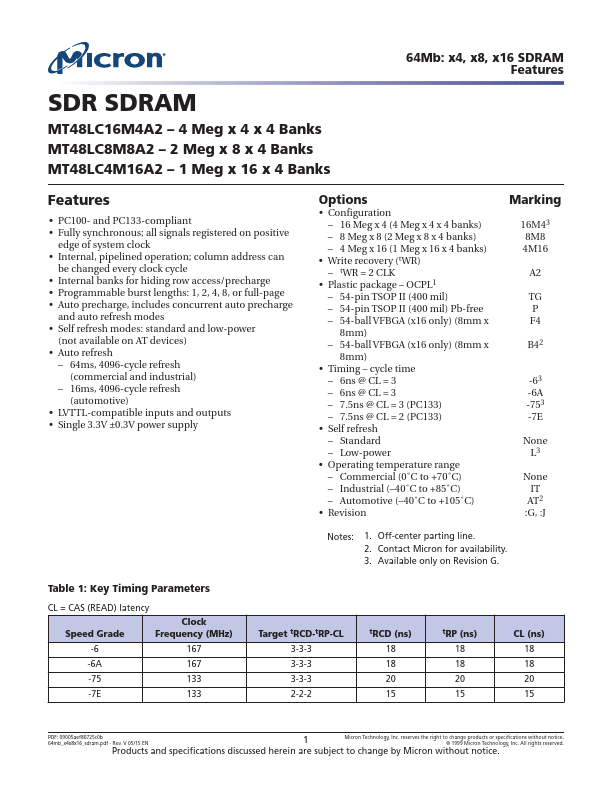

64Mb: x4, x8, x16 SDRAM Features

SDR SDRAM

MT48LC16M4A2

- 4 Meg x 4 x 4 Banks MT48LC8M8A2

- 2 Meg x 8 x 4 Banks MT48LC4M16A2

- 1 Meg x 16 x 4 Banks

Features

- PC100- and PC133-pliant

- Fully synchronous; all signals registered on positive edge of system clock

- Internal, pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access/precharge

- Programmable burst lengths: 1, 2, 4, 8, or full-page

- Auto precharge, includes concurrent auto precharge and auto refresh modes

- Self refresh modes: standard and low-power

(not available on AT devices)

- Auto refresh

- 64ms, 4096-cycle refresh (mercial and industrial)

- 16ms, 4096-cycle refresh...