MT4C16270

MT4C16270 is DRAM 256K X 16 DRAM 5V / EDO PAGE MODE manufactured by Micron Technology.

TECHNOLOGY, INC.

MT4C16270 256K x 16 DRAM

DRAM

Features

- Industry-standard x16 pinouts, timing, functions and packages

- High-performance CMOS silicon-gate process

- Single +5V ±10% power supply-

- Low power, 3mW standby; 300mW active, typical

- All device pins are TTL-patible

- 512-cycle refresh in 8ms (9 row- and 9 column addresses)

- Refresh modes: RAS#-ONLY, CAS#-BEFORE-RAS# (CBR) and HIDDEN

- Extended Data-Out (EDO) PAGE MODE access cycle

- BYTE WRITE and BYTE READ access cycles

256K x 16 DRAM

5V, EDO PAGE MODE

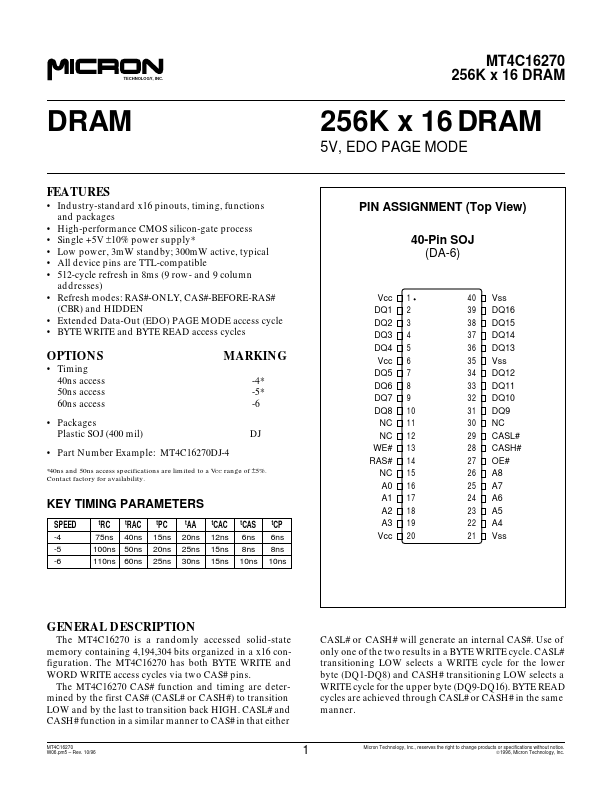

PIN ASSIGNMENT (Top View) 40-Pin SOJ (DA-6)

OPTIONS

- Timing 40ns access 50ns access 60ns access

- Packages Plastic SOJ (400 mil)

MARKING

-4- -5- -6 DJ

- Part Number...