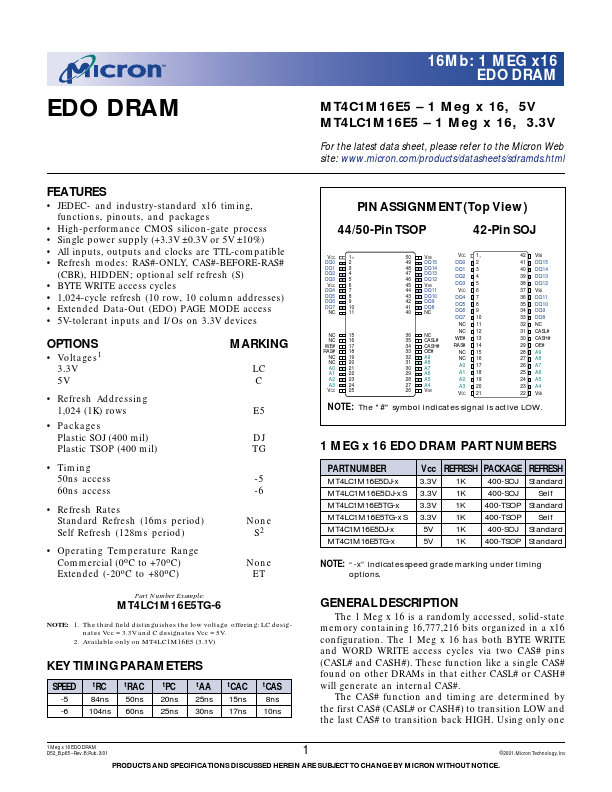

MT4C1M16E5

Description

The 1 Meg x 16 is a randomly accessed, solid-state memory containing 16,777,216 bits organized in a x16 configuration.

Key Features

- JEDEC- and industry-standard x16 timing, functions, pinouts, and packages

- High-performance CMOS silicon-gate process

- Refresh modes: RAS#-ONLY, CAS#-BEFORE-RAS# (CBR), HIDDEN; optional self refresh (S)

- Extended Data-Out (EDO) PAGE MODE access

- 5V-tolerant inputs and I/Os on 3.3V devices

- Voltages 1 3.3V 5V

- Refresh Addressing 1,024 (1K) rows

- Packages Plastic SOJ (400 mil) Plastic TSOP (400 mil)

- Timing 50ns access 60ns access

- Refresh Rates Standard Refresh (16ms period) Self Refresh (128ms period)