MT9LSDT1672 Overview

Key Features

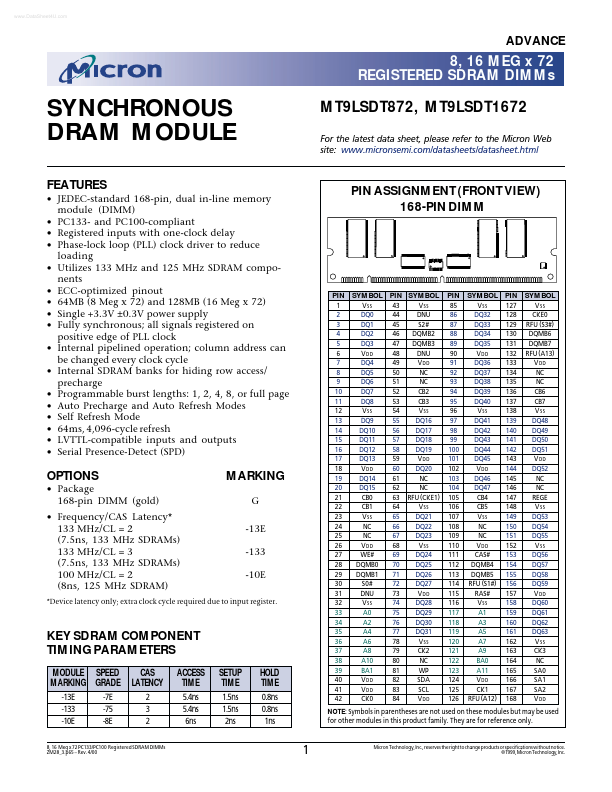

- JEDEC-standard 168-pin, dual in-line memory module (DIMM)

- PC133- and PC100-compliant

- Registered inputs with one-clock delay

- Phase-lock loop (PLL) clock driver to reduce loading

- Utilizes 133 MHz and 125 MHz SDRAM components

- ECC-optimized pinout

- 64MB (8 Meg x

- and 128MB (16 Meg x

- Single +3.3V ±0.3V power supply

- Fully synchronous; all signals registered on positive edge of PLL clock