MT29F256G08CJAAA Overview

Key Features

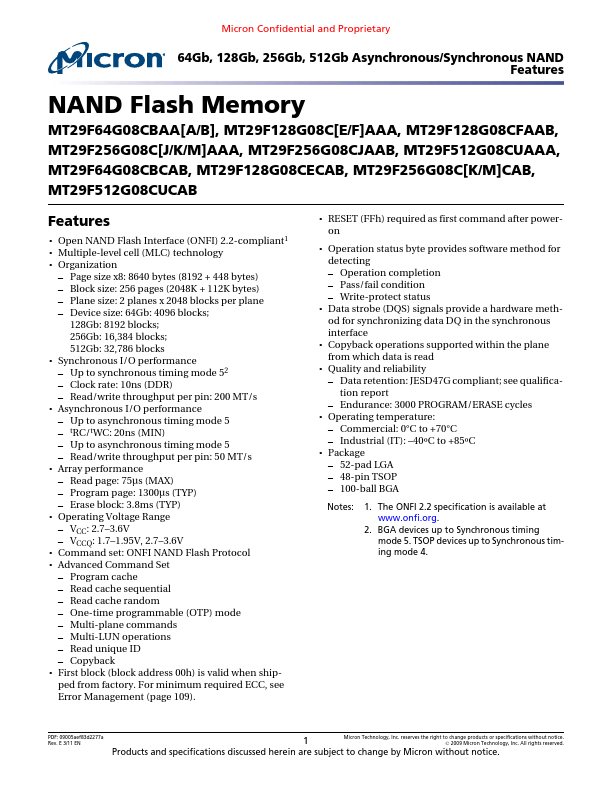

- Open NAND Flash Interface (ONFI) 2.2-compliant1

- Multiple-level cell (MLC) technology

- Synchronous I/O performance – Up to synchronous timing mode 52 – Clock rate: 10ns (DDR) – Read/write throughput per pin: 200 MT/s

- Array performance – Read page: 75µs (MAX) – Program page: 1300µs (TYP) – Erase block: 3.8ms (TYP)

- Command set: ONFI NAND Flash Protocol

- First block (block address 00h) is valid when shipped from factory. For minimum required ECC, see Error Management (page 109)

- RESET (FFh) required as first command after poweron

- Operation status byte provides software method for detecting – Operation completion – Pass/fail condition – Write-protect status

- Data strobe (DQS) signals provide a hardware method for synchronizing data DQ in the synchronous interface

- Copyback operations supported within the plane from which data is read