MT5LC2564

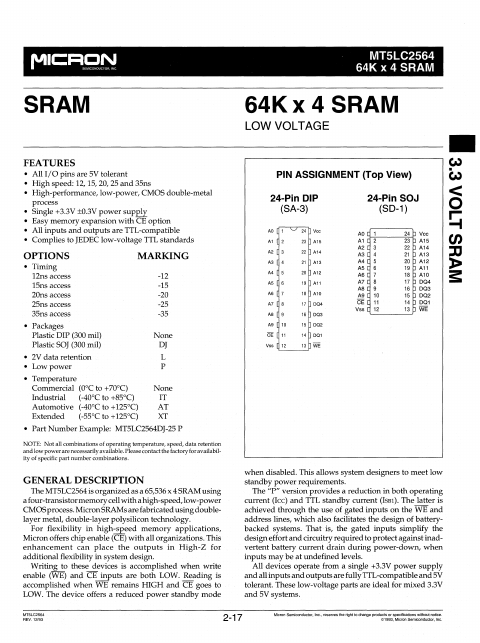

MT5LC2564 is 64K x 4 SRAM manufactured by Micron Technology.

SRAM

Features

- All I/O pins are 5V tolerant

- High speed: 12, 15, 20, 25 and 35ns

- High-performance, low-power, CMOS double-metal process

- Single +3.3V ±O.3V power supply

- Easy memory expansion with CE option

- All inputs and outputs are TTL-patible

- plies to JEOEC low-voltage TTL standards

OPTIONS

MARKING

- Timing 12ns access 15ns access 20ns access 25ns access 35ns access

-12 -15 -20 -25 -35

- Packages Plastic DIP (300 mil)

Plastic SOJ (300 mil)

None OJ

- 2V data retention

- Lowpower

- Temperature mercial (O°C to +70°C) Industrial (-40°C to +85°C) Automotive (-40°C to +125°C) Extended (-55°C to +125°C)

None IT AT XT

- Part Number Example: MT5LC2564DJ-25 P

NOTE: Not all binations of operating temperature, speed, data retention and low power are necessarily available. Please contact the factory for availability of specific part number binations.

GENERAL DESCRIPTION

The MT5LC2564 is organized as a 65,536 x 4 SRAM...