MT61K256M32

Features

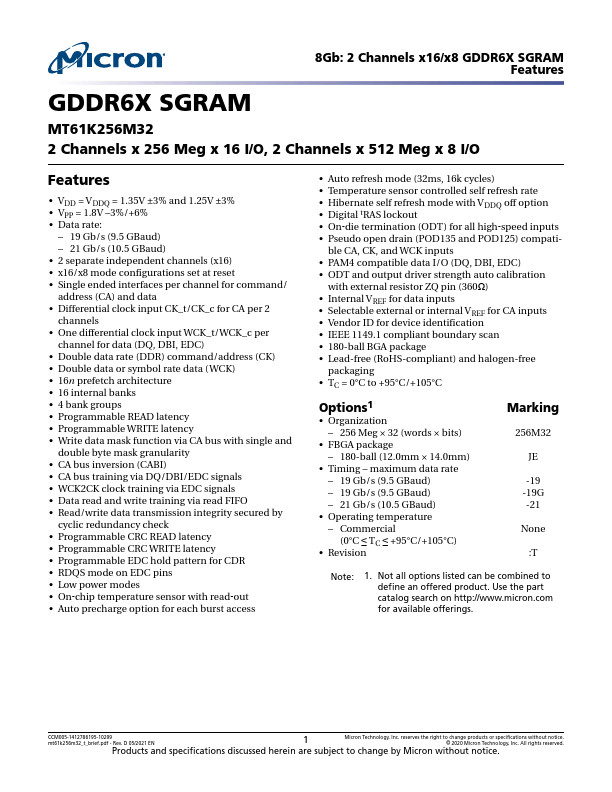

GDDR6X SGRAM

MT61K256M32 2 Channels x 256 Meg x 16 I/O, 2 Channels x 512 Meg x 8 I/O

Features

- VDD = VDDQ = 1.35V ±3% and 1.25V ±3%

- VPP = 1.8V

- 3%/+6%

- Data rate:

- 19 Gb/s (9.5 GBaud)

- 21 Gb/s (10.5 GBaud)

- 2 separate independent channels (x16)

- x16/x8 mode configurations set at reset

- Single ended interfaces per channel for mand/ address (CA) and data

- Differential clock input CK_t/CK_c for CA per 2 channels

- One differential clock input WCK_t/WCK_c per channel for data (DQ, DBI, EDC)

- Double data rate (DDR) mand/address (CK)

- Double data or symbol rate data (WCK)

- 16n prefetch architecture

- 16 internal banks

- 4 bank groups

- Programmable READ latency

- Programmable WRITE latency

- Write data mask function via CA bus with single and double byte mask granularity

- CA bus inversion (CABI)

- CA bus training via DQ/DBI/EDC signals

- WCK2CK clock training via EDC signals

- Data read and write training via read FIFO

- Read/write data transmission integrity secured...