A2F200

A2F200 is SmartFusion Customizable System-on-Chip manufactured by Microsemi.

- Part of the A2F060 comparator family.

- Part of the A2F060 comparator family.

Revision 14

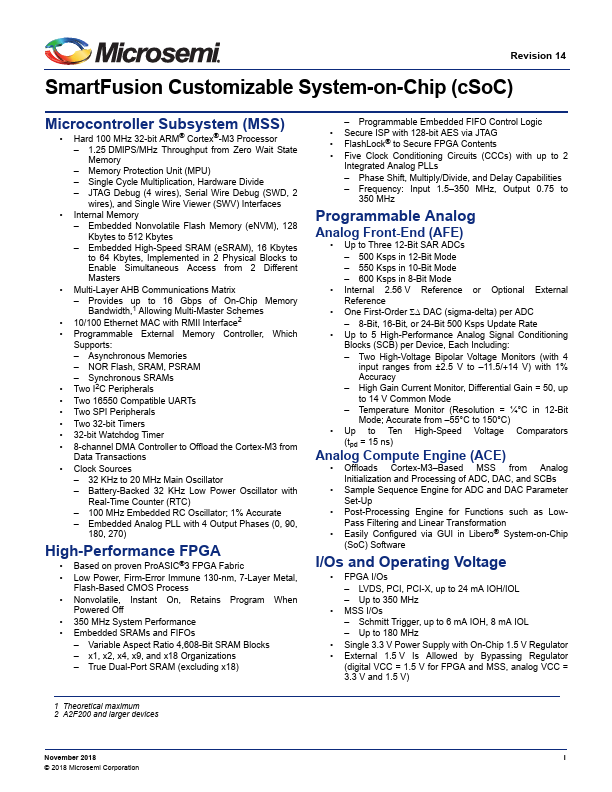

Smart Fusion Customizable System-on-Chip (c So C)

Microcontroller Subsystem (MSS)

- Hard 100 MHz 32-bit ARM® Cortex®-M3 Processor

- 1.25 DMIPS/MHz Throughput from Zero Wait State Memory

- Memory Protection Unit (MPU)

- Single Cycle Multiplication, Hardware Divide

- JTAG Debug (4 wires), Serial Wire Debug (SWD, 2 wires), and Single Wire Viewer (SWV) Interfaces

- Internal Memory

- Embedded Nonvolatile Flash Memory (e NVM), 128 Kbytes to 512 Kbytes

- Embedded High-Speed SRAM (e SRAM), 16 Kbytes to 64 Kbytes, Implemented in 2 Physical Blocks to Enable Simultaneous Access from 2 Different Masters

- Multi-Layer AHB munications Matrix

- Provides up to 16 Gbps of On-Chip Memory Bandwidth,1 Allowing Multi-Master Schemes

- 10/100 Ethernet MAC with RMII Interface2

- Programmable External Memory Controller, Which Supports:

- Asynchronous Memories

- NOR Flash, SRAM, PSRAM

- Synchronous SRAMs

- Two I2C Peripherals

- Two 16550 patible UARTs

- Two SPI Peripherals

- Two 32-bit Timers

- 32-bit Watchdog Timer

- 8-channel DMA Controller to Offload the Cortex-M3 from Data Transactions

- Clock Sources

- 32 KHz to 20 MHz Main Oscillator

- Battery-Backed 32 KHz Low Power Oscillator with

Real-Time Counter (RTC)

- 100 MHz Embedded RC Oscillator; 1% Accurate

- Embedded Analog PLL with 4 Output Phases (0, 90,

180, 270)

High-Performance FPGA

- Based on proven Pro ASIC®3 FPGA Fabric

- Low Power, Firm-Error Immune 130-nm, 7-Layer Metal, Flash-Based CMOS Process

- Nonvolatile, Instant On, Retains Program When Powered Off

- 350 MHz System Performance

- Embedded SRAMs and FIFOs

- Variable Aspect Ratio 4,608-Bit SRAM Blocks

- x1, x2, x4, x9, and x18 Organizations

- True Dual-Port SRAM (excluding...