EDI88512C Description

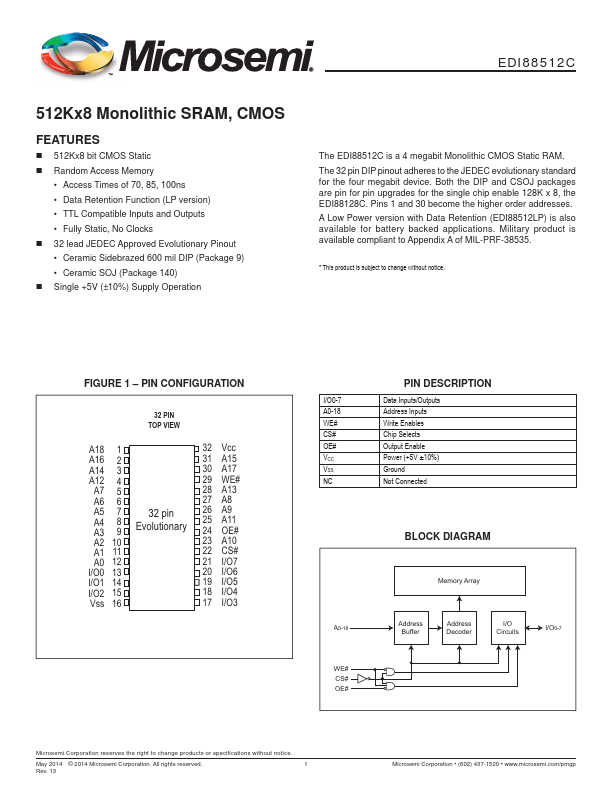

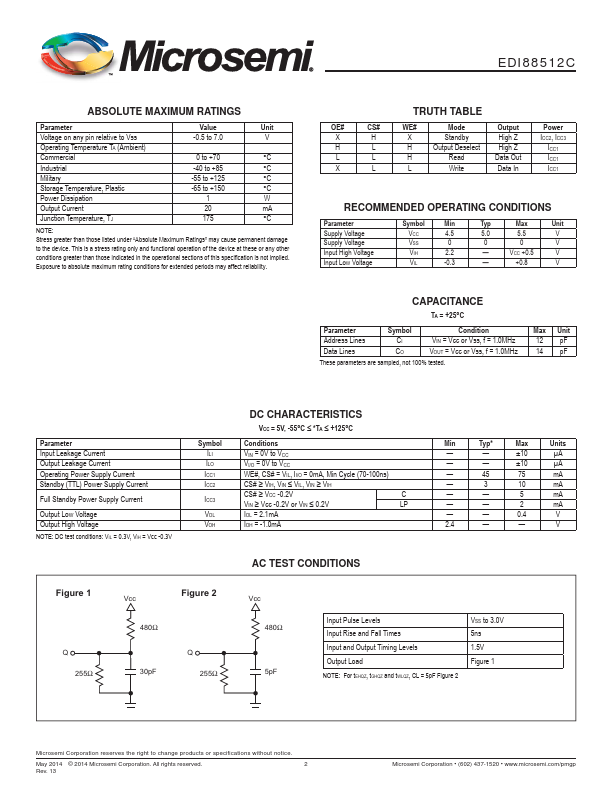

Data Inputs/Outputs Address Inputs Write Enables Chip Selects Output Enable Power (+5V ±10%) Ground Not Connected A0-18 WE# CS# OE# BLOCK DIAGRAM Memory Array Address Buffer Address Decoder I/O Circuits I/O0-7 Microsemi Corporation reserves the right to change products or specifications without notice. May 2014 © 2014 Microsemi Corporation. Stress greater than those listed under “ Ratings” may cause permanent damage...

EDI88512C Key Features

- 512Kx8 bit CMOS Static - Random Access Memory

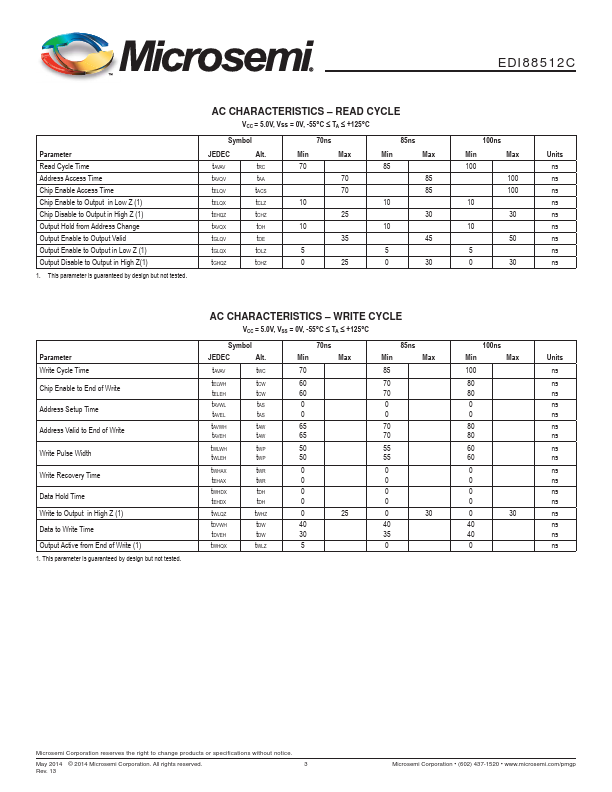

- Access Times of 70, 85, 100ns

- Data Retention Function (LP version)

- TTL patible Inputs and Outputs

- Fully Static, No Clocks - 32 lead JEDEC Approved Evolutionary Pinout

- Ceramic Sidebrazed 600 mil DIP (Package 9)

- Ceramic SOJ (Package 140) - Single +5V (±10%) Supply Operation

EDI88512C Applications

- This product is subject to change without notice