MAX3674

Overview

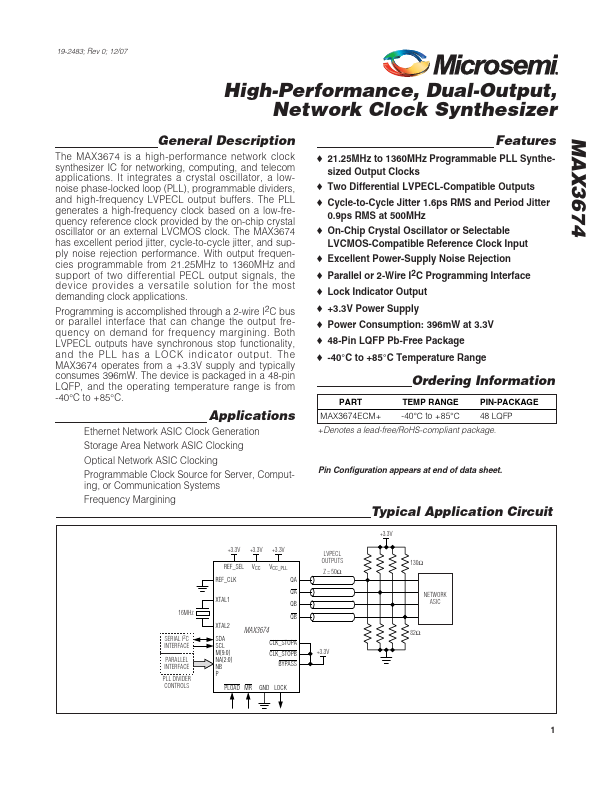

The MAX3674 is a high-performance network clock synthesizer IC for networking, computing, and telecom applications. It integrates a crystal oscillator, a lownoise phase-locked loop (PLL), programmable dividers, and high-frequency LVPECL output buffers.

- 21.25MHz to 1360MHz Programmable PLL Synthesized Output Clocks

- Two Differential LVPECL-Compatible Outputs

- Cycle-to-Cycle Jitter 1.6ps RMS and Period Jitter

- 9ps RMS at 500MHz

- On-Chip Crystal Oscillator or Selectable LVCMOS-Compatible Reference Clock Input

- Excellent