ZL30145

ZL30145 is SyncE (10 GbE) SONET/SDH Rate Conversion and Jitter Attenuator PLL manufactured by Microsemi.

Features

- Can be used in systems to support the requirements of ITU-T G.8262 for synchronous Ethernet Equipment slave Clocks (EEC option 1 and 2)

- Meets jitter generation requirements of Telcordia GR-253-CORE for OC-192, OC-48, OC-12 and OC-3 rates

- Meets jitter generation requirements of ITU-T G.813 for STM-64, STM-16, STM-4 and STM-1 rates

- Synchronizes to standard tele or Ethernet clock and provides jitter filtered output clock for SONET/SDH and Synchronous Ethernet line cards

- Synchronizes to tele reference clocks (2 k Hz, N- 8 k Hz up to 77.76 MHz, 155.52 MHz) or to Ethernet reference clocks (25 MHz, 50 MHz, 62.5 MHz, 125 MHz)

- Generates standard SONET/SDH clock rates (e.g., 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, 622.08 MHz) or Ethernet clock rates (e.g., 25 MHz, 50 MHz, 125 MHz, 156.25 MHz, 312.5 MHz) for synchronizing Ethernet PHYs

- Selectable loop bandwidth of 14 Hz, 28 Hz, or 890 Hz

March 2013

Ordering Information ZL30145GGG 64 Pin CABGA Trays ZL30145GGG2 64 Pin CABGA- Trays

- Pb Free Tin/Silver/Copper -40o C to +85o C

- Configurable through a serial interface (SPI or I2C)

- DPLL can be configured to provide synchronous or asynchronous clock outputs

- Supports IEEE 1149.1 JTAG Boundary Scan

Applications

- ITU-T G.8262 Line Cards which support 1 Gb E and 10 Gb E interfaces

- SONET line cards up to OC-192

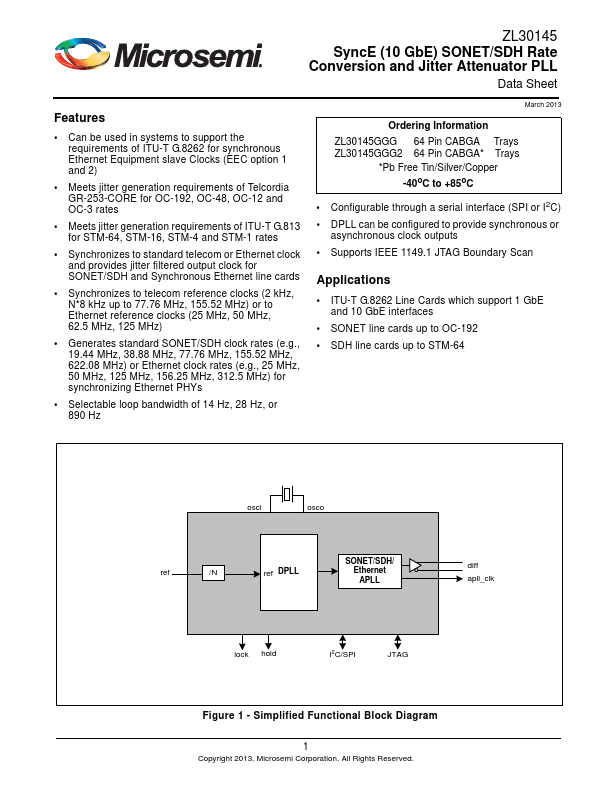

- SDH line cards up to STM-64 osci osco ref

/N ref DPLL

SONET/SDH/ Ethernet APLL diff apll_clk lock hold

I2C/SPI

JTAG

Figure 1

- Simplified Functional Block Diagram

Copyright 2013, Microsemi Corporation. All Rights Reserved.

Data Sheet

Table of Contents

1.0 Pin Diagram

- -

- -

- -

- -

- -

- -

- - . . . . 14

2.0 High Level Overview

- -

- -

-...