ZL30157

Key Features

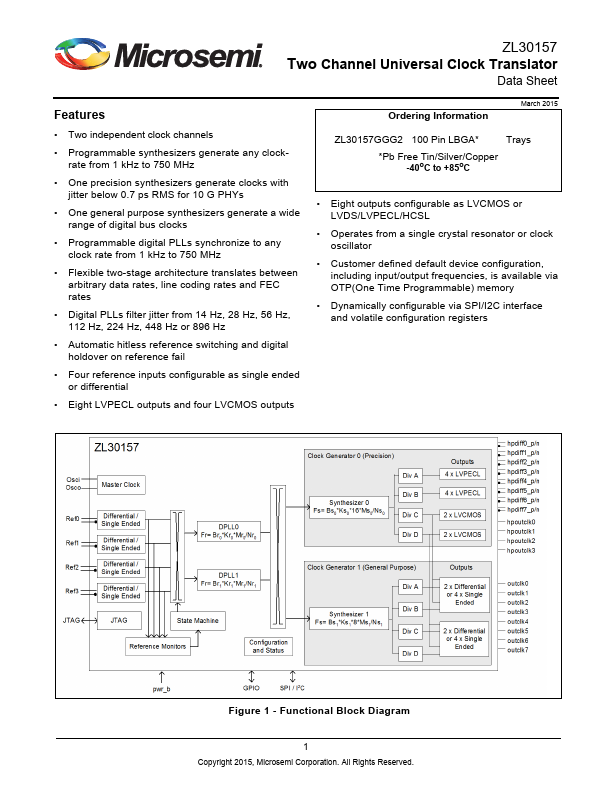

- Two independent clock channels

- Programmable synthesizers generate any clockrate from 1 kHz to 750 MHz

- One precision synthesizers generate clocks with jitter below 0.7 ps RMS for 10 G PHYs

- One general purpose synthesizers generate a wide range of digital bus clocks

- Programmable digital PLLs synchronize to any clock rate from 1 kHz to 750 MHz

Applications

- 10 Gigabit line cards