ZL30182

Key Features

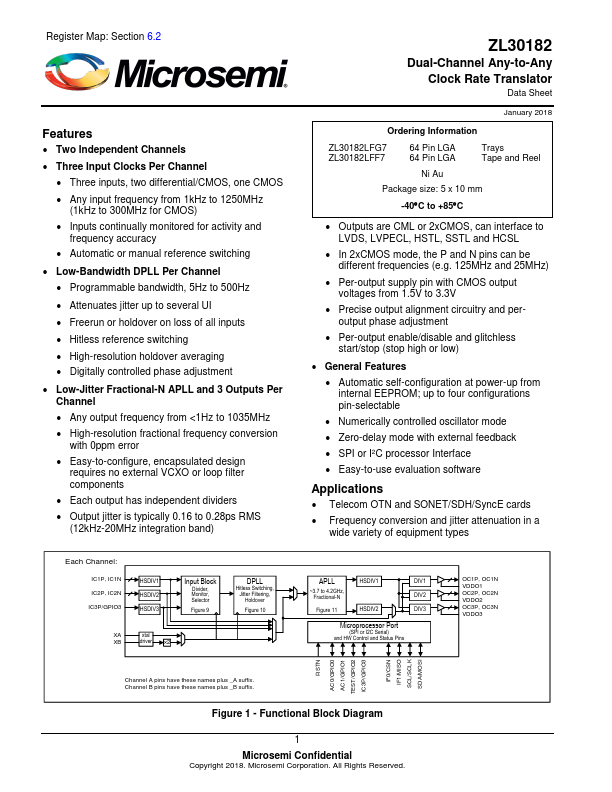

- Two Independent Channels

- Three Input Clocks Per Channel

- Three inputs, two differential/CMOS, one CMOS

- Any input frequency from 1kHz to 1250MHz (1kHz to 300MHz for CMOS)

- Inputs continually monitored for activity and frequency accuracy

Applications

- Tele OTN and SONET/SDH/SyncE cards