MT90500

Overview

- AAL1 Segmentation and Reassembly device compatible with Structured Data Transfer (SDT) as per ANSI T1.630 and ITU I.363 standards

- Transports 64kbps and N x 64kbps traffic over ATM AAL1 cells (also over AAL5 or AAL0)

- Simultaneous processing of up to 1024 bidirectional Virtual Circuits

- Flexible aggregation capabilities (Nx64) to allow any combination of 64 kbps channels while maintaining frame integrity (DS0 grooming)

- Support for clock recovery - Adaptive Clock Recovery, Synchronous Residual Time Stamp (SRTS), or external

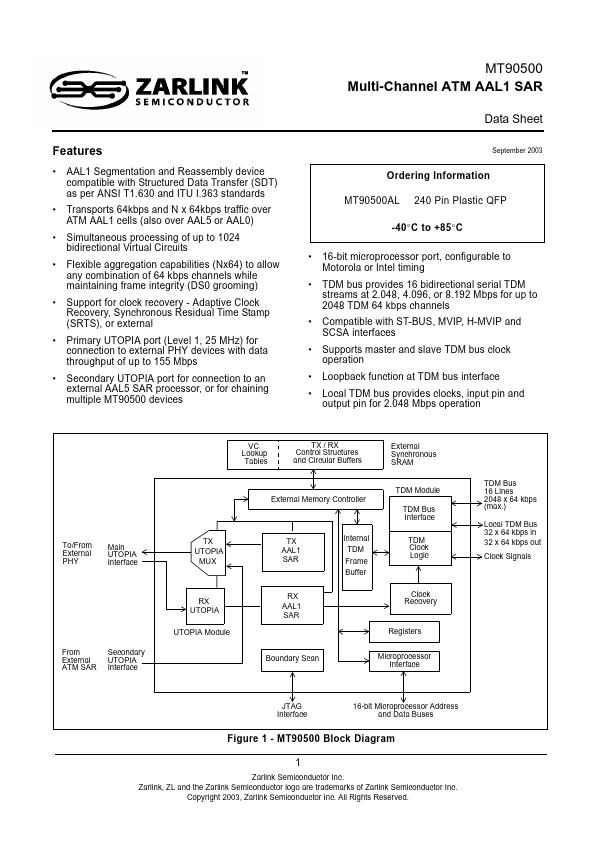

- Primary UTOPIA port (Level 1, 25 MHz) for connection to external PHY devices with data throughput of up to 155 Mbps

- Secondary UTOPIA port for connection to an external AAL5 SAR processor, or for chaining multiple MT90500 devices MT90500 Multi-Channel ATM AAL1 SAR Data Sheet September 2003