| Part | PDSP16116MCGGDR |

|---|---|

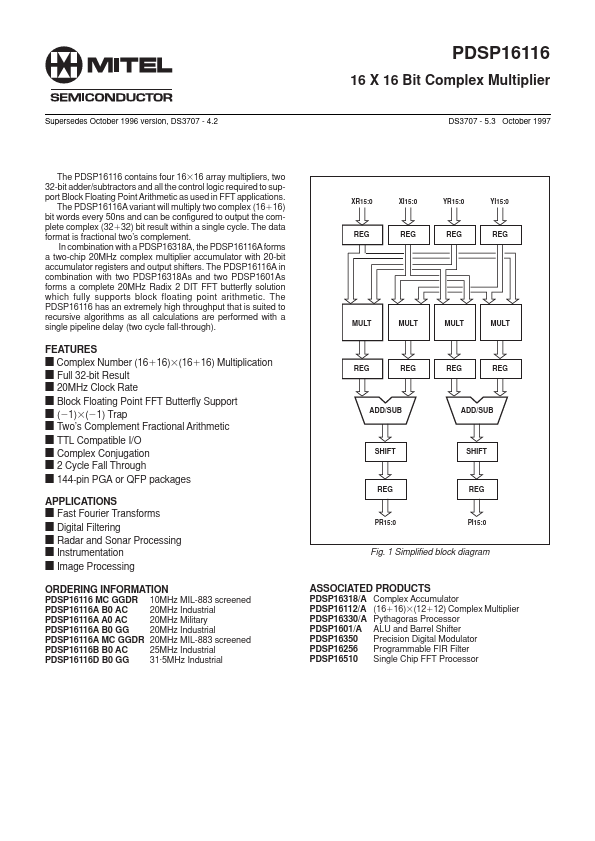

| Description | 16 X 16 Bit Complex Multiplier |

| Manufacturer | Mitel Networks Corporation |

| Size | 270.67 KB |

Related Datasheets

- AD835 — Analog Devices — 4-Quadrant Multiplier

- HA1-2556883 — Intersil — Wideband Four Quadrant Analog Multiplier (Voltage Output)

- ZL30251 — Microsemi — 3-Output Any-to-Any Clock Multiplier and Frequency Synthesizer