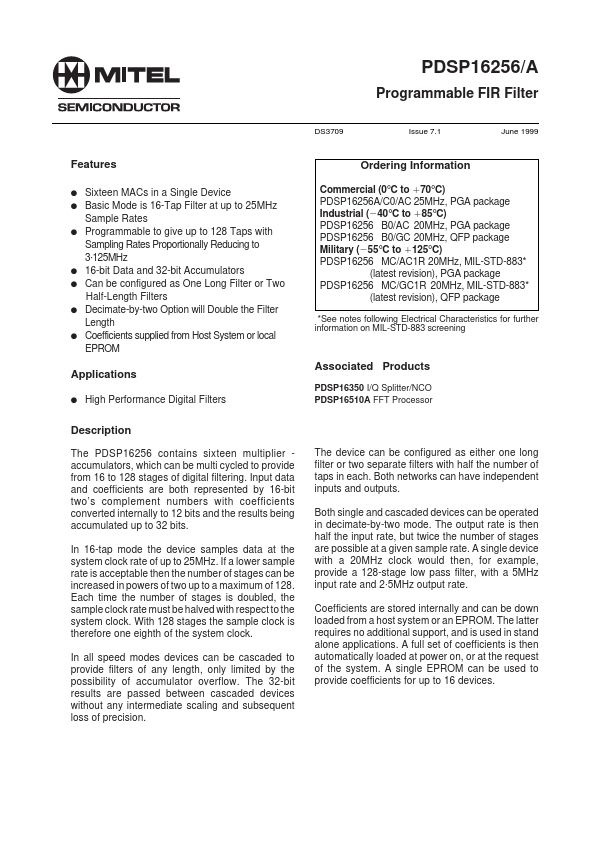

PDSP16256AC1R Overview

Description

The PDSP16256 contains sixteen multiplier accumulators, which can be multi cycled to provide from 16 to 128 stages of digital filtering. Input data and coefficients are both represented by 16-bit two’s complement numbers with coefficients converted internally to 12 bits and the results being accumulated up to 32 bits.