M2S12D30TP

M2S12D30TP is 512M Double Data Rate Synchronous DRAM manufactured by Mitsubishi Electric.

- Part of the M2S comparator family.

- Part of the M2S comparator family.

DDR SDRAM (Rev.1.1) Feb.ELECTRIC '02

MITSUBISHI

MITSUBISHI LSIs

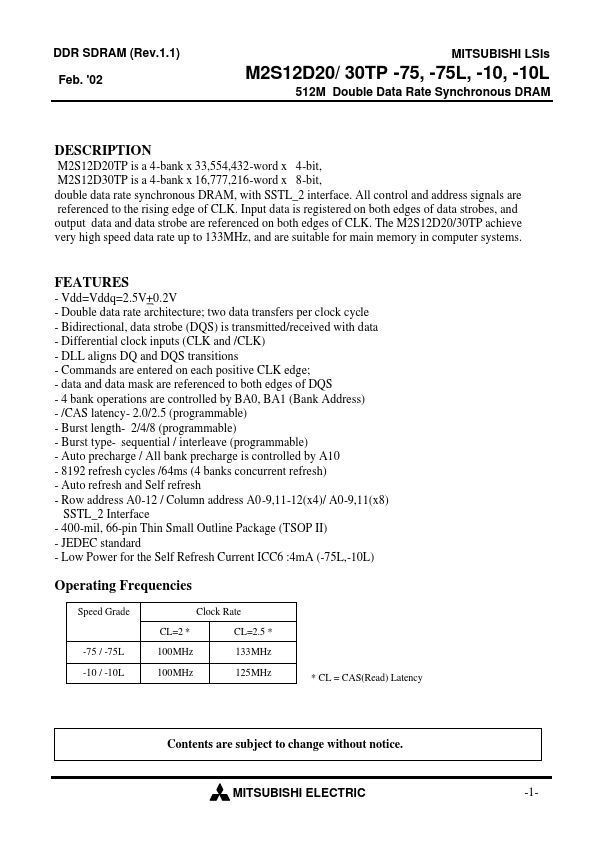

M2S12D20/ 30TP -75, -75L, -10, -10L

512M Double Data Rate Synchronous DRAM

DESCRIPTION

M2S12D20TP is a 4-bank x 33,554,432-word x 4-bit, M2S12D30TP is a 4-bank x 16,777,216-word x 8-bit, double data rate synchronous DRAM, with SSTL_2 interface. All control and address signals are referenced to the rising edge of CLK. Input data is registered on both edges of data strobes, and output data and data strobe are referenced on both edges of CLK. The M2S12D20/30TP achieve very high speed data rate up to 133MHz, and are suitable for main memory in puter systems.

Features

- Vdd=Vddq=2.5V+0.2V

- Double data rate architecture; two...