M2V28S40TP

DESCRIPTION

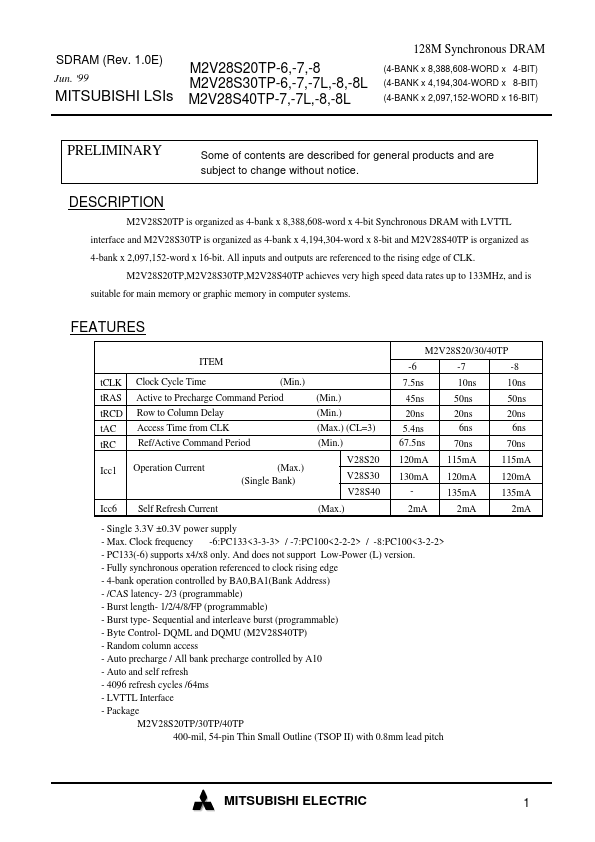

M2V28S20TP is organized as 4-bank x 8,388,608-word x 4-bit Synchronous DRAM with LVTTL interface and M2V28S30TP is organized as 4-bank x 4,194,304-word x 8-bit and M2V28S40TP is organized as 4-bank x 2,097,152-word x 16-bit. All inputs and outputs are referenced to the rising edge of CLK. M2V28S20TP,M2V28S30TP,M2V28S40TP achieves very high speed data rates up to 133MHz, and is suitable for main memory or graphic memory in puter systems.

FEATURES

M2V28S20/30/40TP ITEM t CLK t RAS t RCD t AC t RC Icc1 Clock Cycle Time Row to Column Delay Access Time from CLK Ref/Active mand Period Operation Current (Max.) (Single Bank) (Max.) (Min.) (Min.) (Min.) (Max.) (CL=3) (Min.) V28S20 V28S30 V28S40 Icc6 Self Refresh Current -6 7.5ns 45ns 20ns 5.4ns 67.5ns 120m A 130m A 2m A -7 10ns 50ns 20ns 6ns 70ns 115m A 120m A 135m A 2m A -8 10ns 50ns 20ns 6ns 70ns 115m A 120m A 135m A 2m A

Active to Precharge mand Period

- Single 3.3V ±0.3V power supply

- Max. Clock frequency -6:PC133<3-3-3> / -7:PC100<2-2-2>...