V54C3256164VBUT

V54C3256164VBUT is LOW POWER 256Mbit SDRAM manufactured by Mosel Vitelic Corp.

Features

- 4 banks x 4Mbit x 16 organization

- High speed data transfer rates up to 166 MHz

- Full Synchronous Dynamic RAM, with all signals referenced to clock rising edge

- Single Pulsed RAS Interface

- Data Mask for Read/Write Control

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 3

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length: 1, 2, 4, 8 for Sequential Type 1, 2, 4, 8 for Interleave Type

- Multiple Burst Read with Single Write Operation

- Automatic and Controlled Precharge mand

- Random Column Address every CLK (1-N Rule)

- Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 8192 cycles/64 ms

- Available in 54-Ball SOC BGA/ 54-Pin TSOP II

- LVTTL Interface

- Single +3.3 V ±0.3 V Power Supply

- Low Power Self Refresh Current

- L-version 1.0m A

- U-version 0.6m A

Description

The V54C3256164VBUC/T is a low power four bank Synchronous DRAM organized as 4 banks x 4Mbit x 16. The V54C3256164VBUC/T achieves high speed data transfer rates up to 166 MHz by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock All of the control, address, data input and output circuits are synchronized with the positive edge of an externally supplied clock. Operating the four memory banks in an interleaved fashion allows random access operation to occur at higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 166 MHz is possible depending on burst length, CAS latency and speed grade of the device. The V54C3256164VBUC/T is ideally suited for high performance, low power systems such as PDA, mobile phone, DSC, and other battery backup applications.

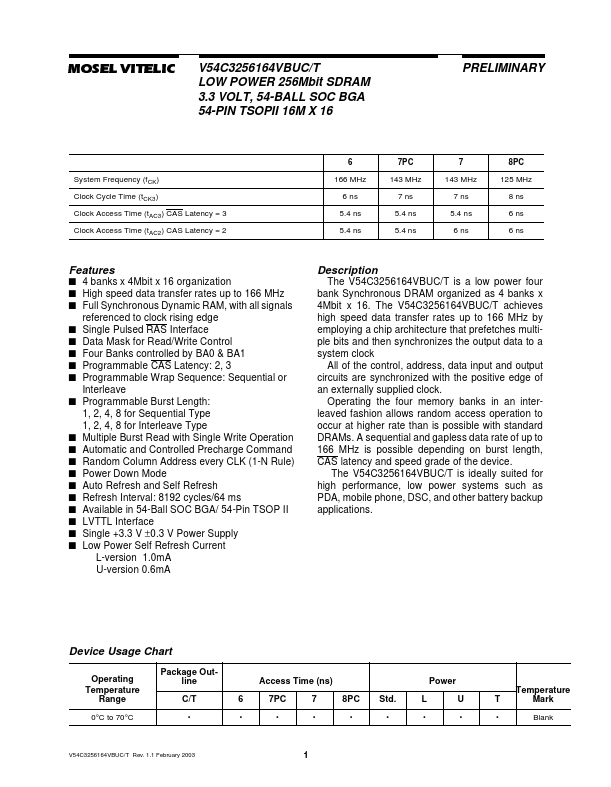

Device Usage Chart

Operating Temperature Range

0°C to 70°C

Package Outline C/T

- Access Time (ns) 6

- Power 8PC

- 7PC

- 7

- Std.

- L

- U

- T

- Temperature Mark

Blank

V54C3256164VBUC/T Rev. 1.1 February...